Grid

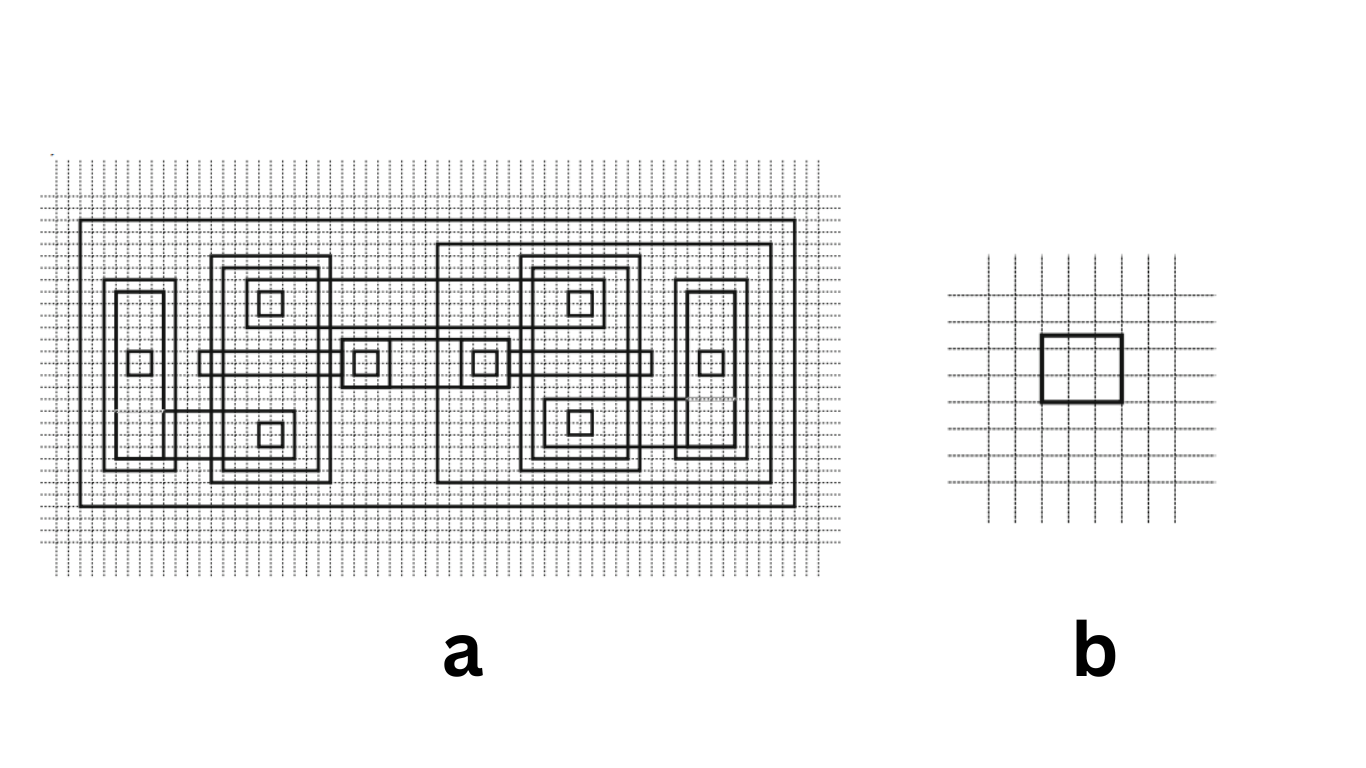

In layout, there’s something called the “grid.” Look at Figure 1a to see how all the designs have to match the grid. You need to know how big the smallest grid is and tell the layout editor before you start. It’s really tough to fix a shape that’s not on the grid, like in Figure 1b.

The grid might be different for each layer because it’s cheaper to make a mask with a wider grid than a close one. For example, fine details like gates and contact holes might fit a small 0.01m grid, but bigger parts like the N-well or top metal layer could use a wider 0.05m grid.

Also, it’s important to check if you can use 45-degree diagonal designs or any other angles. If you can, you need to figure out how to handle the grid for those situations.