Memory Compiler

To achieve flexibility in terms of memory size, memory array organization (rows and columns), and physical layout orientation of memory blocks, a tool called a memory compiler is employed. System-on-Chip (SOC) designs are available in pre-designed and pre-validated forms tailored to specific manufacturing processes. These memory instances are optimized to meet the area, speed, and power requirements ideal for high-performance applications.

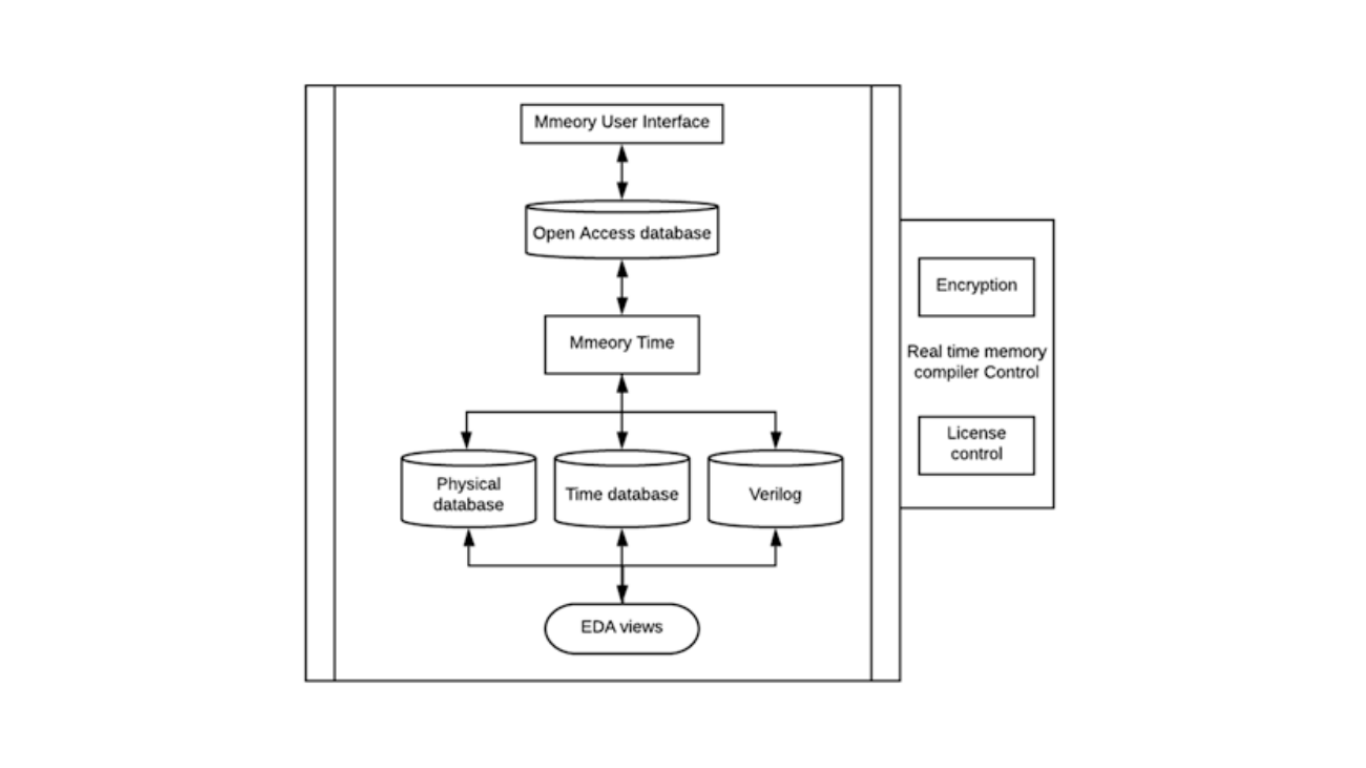

Memory Compiler Architecture

Memory compilers are provided by memory vendors for specific target technology nodes. These compilers utilize standard bit cells provided by foundries to ensure reliability and high yield. They dynamically generate memory design files, including layout designs, according to the user’s configuration preferences. This includes options for integrating features like error-correcting code (ECC) for repairable memories, built-in self-test (BIST), redundancy, and support for advanced power management modes such as Light Sleep, Deep Sleep, and Shut Down. The memory compilers utilize proprietary circuit design techniques, including high-speed sense amplifiers, fast clocking, and rapid bit line recovery, to achieve the high-speed demands of modern high-performance applications.

Memory Compilers Features

- Create memory instances with integrated logic to enable built-in self-test (BIST), ECC, and redundancy for repair, based on user configuration.

- Generate memory models with various aspect ratios, test benches, liberty files, GDS (Graphic Data System), LEF (Library Exchange Format), and other views for integration into the SOC design.

- Allow users to choose between high-performance (access time) or high-yield factors by selecting process-sigma characterization and read-write margin settings.

- Fully automate the generation of required views for industry-standard Electronic Design Automation (EDA) tools and SOC design integration.

- Provide an easy-to-use graphical user interface (GUI) for batch mode memory generation with rapid execution time.

- Ensure the security of physical design files through encryption, as they are characterized for specific performance levels.

- Generate PDF datasheets for memory instances.

- Operate independently from EDA tools.

- Offer detailed user manuals, training resources, and tutorials.

- Enable real-time instance-based characterization.

A typical memory compiler architecture is depicted in the above figure, illustrating the flow of processes and interactions within the memory compiler tool.