Metastability

The designed circuit can get into states where the signals can settle to an intermediate value between logic 0 and logic 1, this is called a metastable state.

What is Metastability #

When this occurs, the system’s logic circuit may not return to a stable state and may instead become locked in a metastable state, which might result in fatal mistakes. When the specs’ timing criteria are not met, something will occur. It is good knowledge that flip-flops require setup and hold times in order to operate correctly.

A flip-setup flop’s time and hold time are the time periods during which the data should stabilize prior to the clock edge and following the clock edge, respectively. The setup and hold times of the flip-flop must be met in order for them to operate correctly.

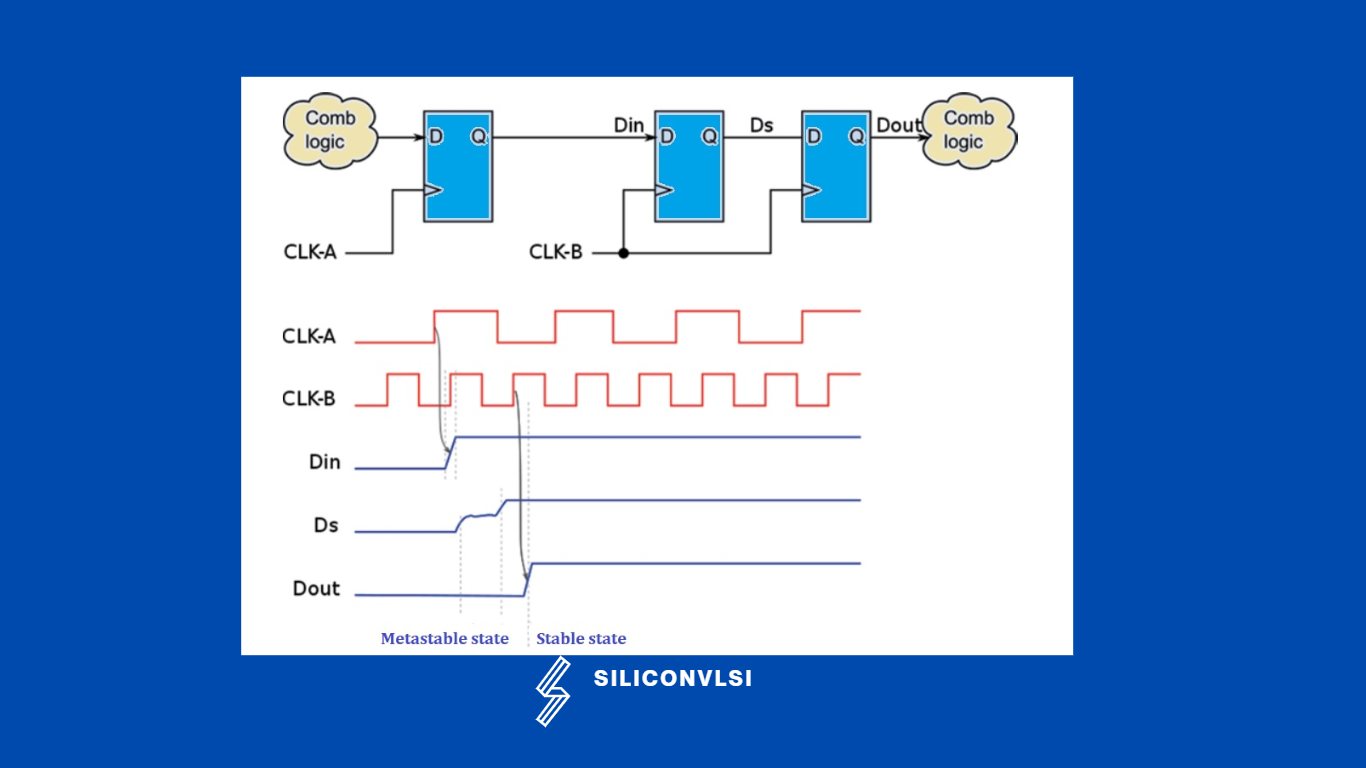

If this condition is not satisfied, the circuit may reach a metastable state and frequently won’t return to a stable one. This can be prevented by using two flip-flops in double synchronization with the clock signal to send the signals under consideration through two or more of them, allowing the system adequate time to reach a stable state. The metastable and stable states of the logic path are depicted in Figure.