Netlist

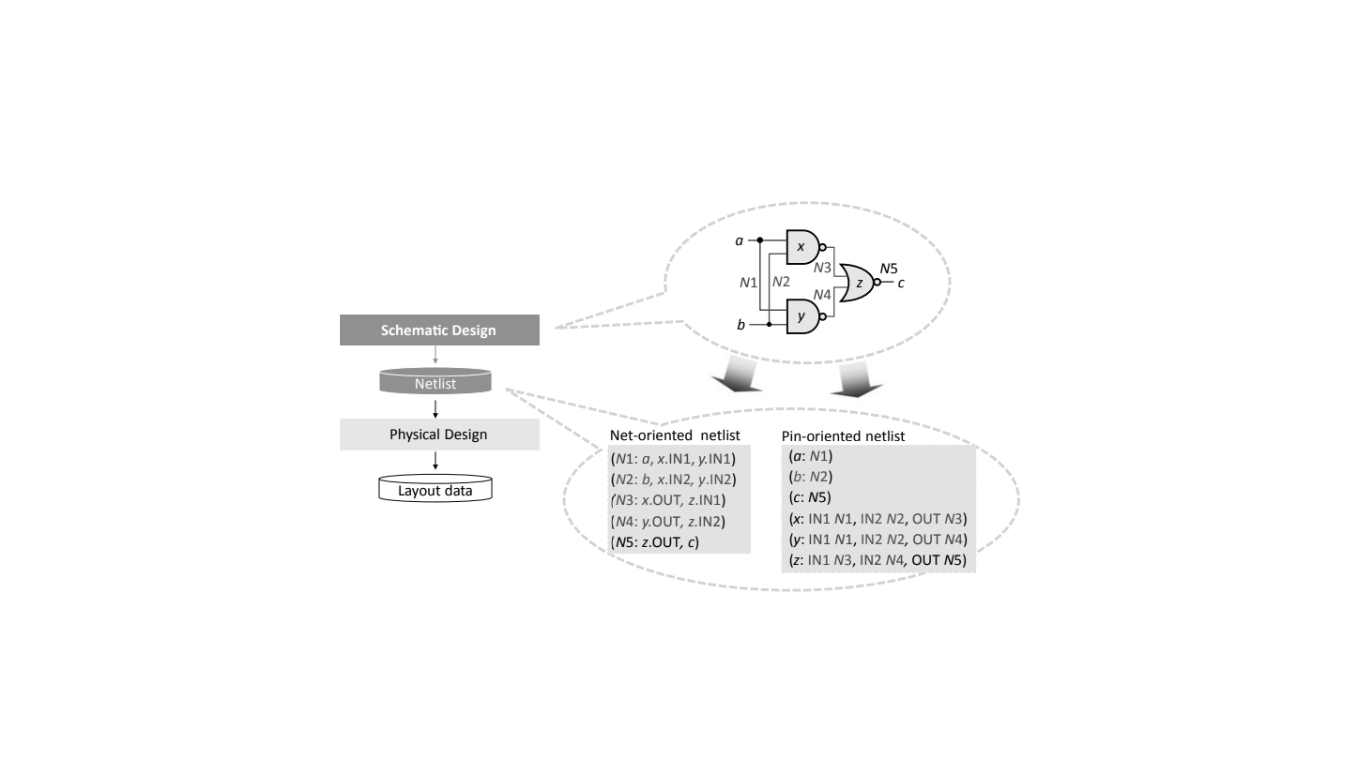

Netlists play a crucial role in bridging the gap between the schematic design entry and the subsequent physical design of a circuit. Here’s an overview of their significance and how they are generated.

Before generating a netlist, the schematic design undergoes a thorough check for errors and inconsistencies. Electrical Rule Check (ERC) programs are commonly used for this purpose. ERC identifies issues like unconnected inputs and multiple instances with identical names. Additionally, circuit simulation tools such as SPICE can be used to verify the correctness of the schematic.

Types of Netlists

Netlists can be generated in two primary formats: flat or hierarchical. The choice depends on the complexity of the design and the organization of the schematic. Hierarchical netlists are used when the schematic is organized into a hierarchical structure. In hierarchical netlists, the hierarchical information is preserved using path structures in device and node (net) names.

Information contained in a Netlist

The content of a netlist may vary based on its intended use. When generating a netlist for simulation purposes, it includes not only node and device information but also control information. Control information typically consists of model details required for simulation. For instance, a SPICE netlist contains both the circuit information and the necessary control information for simulation.

Net-Oriented vs. Pin-Oriented Lists

Netlists can be categorized into net-oriented and pin-oriented lists. Net-oriented netlists primarily focus on signal nets (nodes) and the connections between them. They are commonly used for simulation and analysis. In contrast, pin-oriented netlists emphasize the physical pins of devices and the nets they connect to. Pin-oriented netlists are more relevant for physical design processes, such as layout generation.

In summary, netlists serve as a vital link between the schematic design and the physical implementation of a circuit. They ensure that the design is accurately translated into a format that can be further analyzed, simulated, or used for physical layout generation, depending on the specific requirements of the design process.