What is Nwell Antenna Effect

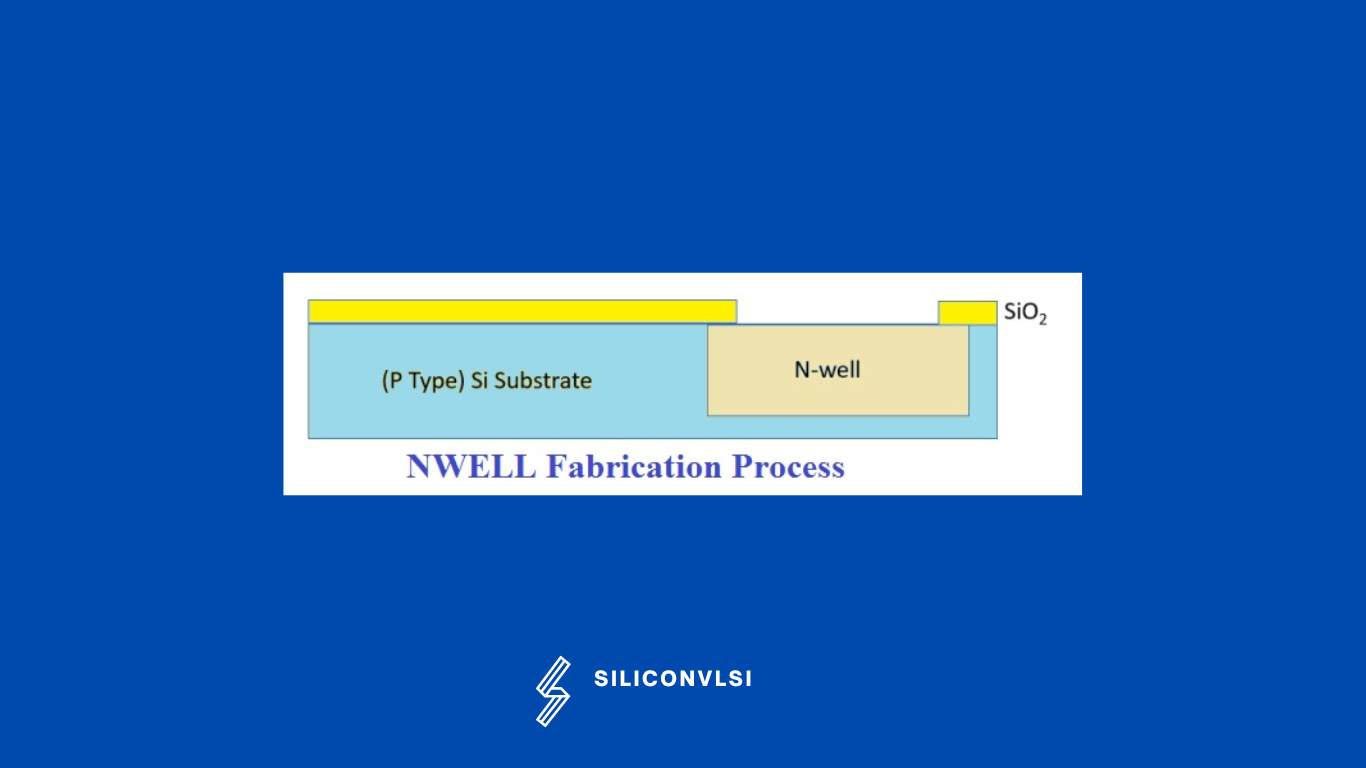

Nwell is fabricated by ion Implantation, During the fabrication process, some charges are accumulated on Nwell. The charge build-up may not be from the gate to the body in CMOS, but It can also be the body(nwell) to the gate of a MOSFET. So we can say that during fabrication, before contact and metal, there can be a charge build-up on the body of a pMOS transistor (nwell) relative to the gate. Now after nwell fabrication, the next step is gate(poly) fabrication for self-alignment purposes, now if the charge on nwell is huge, then it may, damage the gate oxide under the poly, this is called as nwell antenna Effect in VLSI.

How to Solve Nwell Antenna Effect

- We should put N+(bulk connection) to Nwell.

- The N+/P diode should provide enough leakage to prevent any damage to the gate oxide.