Latch-Up in CMOS: Causes, Effects, and Prevention

Latch-up is a problem that occurs in CMOS devices when parasitic transistors become active under certain conditions. When this happens, the device goes into a state of self-sustaining conduction, which can lead to damage. Latch-up can happen in CMOS devices due to various factors, such as excessive power supply voltage, high input voltage, high input current, and high-temperature operation. Once a device goes into latch-up, it can be challenging to bring it out of the state without causing damage.

Causes of Latch-Up

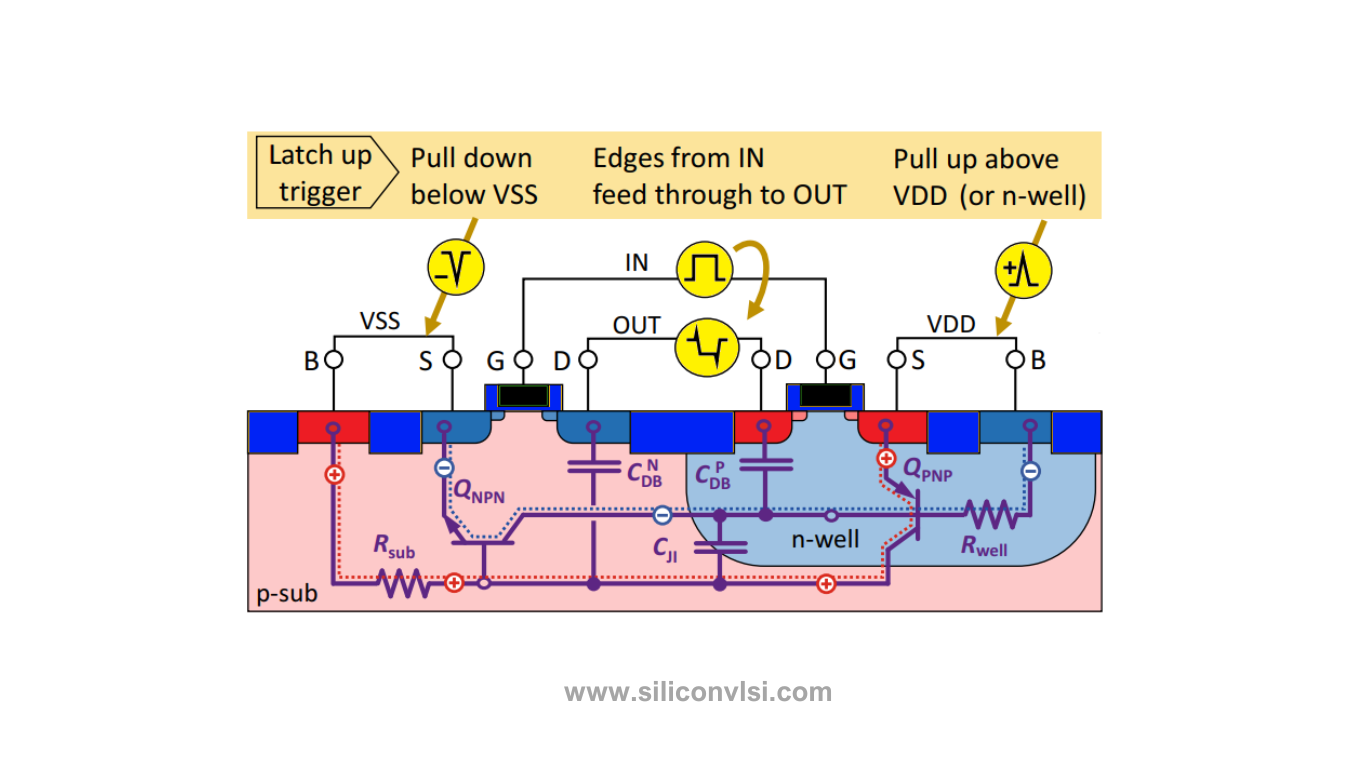

The primary reason for latch-up in CMOS devices is the parasitic bipolar junction transistors (BJTs) that exist in the fabrication process. These BJTs are unintentionally formed but can become active under certain conditions. BJTs can form between the p-type substrate and the n-well region, which can lead to a feedback loop, causing the device to go into latch-up.

Excessive power supply voltage, high input voltage, high input current, and high temperature can also cause latch-up. If the device exceeds its rated maximum specifications, the BJTs can become active, resulting in a latch-up.

- Impact of Process Parameters

- Latch-up susceptibility depends on process parameters

- Factors that affect latch-up include:

- Doping concentration

- Junction depth

- Implant energy

- Gate oxide thickness

- Substrate resistance

- Interconnect layout

- Higher device density and smaller geometries increase latch-up susceptibility

Effects of Latch-Up

When latch-up occurs, the device can go into a state of self-sustaining conduction, which can lead to significant damage or even complete system failure. Since latch-up can create a feedback loop, it can cause power dissipation, resulting in overheating. Overheating can cause permanent damage to the device, and in worst-case scenarios, it can lead to a fire.

- Impact of Latch-Up on System Performance

- Latch-up can cause system failure and reduce system performance

- Impact on system performance includes:

- Increased power consumption

- Signal distortion

- Delay variation

- Noise susceptibility

Prevention of Latch-Up

Several methods can prevent latch-up in CMOS devices. One effective method is to use layout techniques that minimize parasitic elements. Layouts should maintain symmetry and avoid sharp corners. Additionally, designers can utilize guard rings, which are heavily doped p-type regions that surround the device in question, and prevent latch-up. Another technique is to keep the power supply and input voltage within safe operating limits. Designers can use voltage regulators to maintain stable power supplies, preventing excessive voltage. Using these techniques can mitigate the causes of latch-up and prevent the damage it causes.

- Parasitic BJTs can be disconnected from power rails by:

- Reducing substrate doping concentration

- Increasing substrate resistance

- Implanting additional N-well or P-well

- Design techniques to prevent latch-up:

- Avoid large current loops

- Increase the distance between signal lines and power rails

- Use guard rings, dummy cells, or dummy transistors

- Add ESD (Electrostatic Discharge) protection circuits

Conclusion

Latch-up is a serious problem in CMOS devices that can cause complete system failure. The causes can vary, from parasitic BJTs to excessive power supply voltage and high temperature. Effective prevention methods include layout techniques, guard rings, and input voltage regulation. As a content writer in the tech industry, it’s important to understand the challenges and solutions that affect the manufacturing of devices.

FAQs

Can latch-up occur in all CMOS devices?

Latch-up can occur in any CMOS device, but some devices are more prone than others. The susceptibility to latch-up depends on the specific design of the device and the operating conditions.

What causes the overheating in devices affected by latch-up?

When latch-up occurs, the device goes into self-sustaining conduction, which can cause power dissipation. The excess power dissipation results in overheating, which can cause permanent damage to the device.

What is the primary technology used in the manufacturing of processors?

CMOS (complementary metal-oxide-semiconductor) is the primary technology used in the manufacturing of processors.

Can guard rings completely prevent latch-up from occurring?

Although guard rings are effective in preventing latch-up, they cannot entirely eliminate the possibility of it occurring. Proper design strategies should also involve other prevention methods to ensure safe operation.

How can voltage regulation prevent latch-up?

Using voltage regulators can maintain stable power supplies, preventing devices from exceeding their rated maximum specifications, which can cause latch-up.