What is a Composite Layouts?

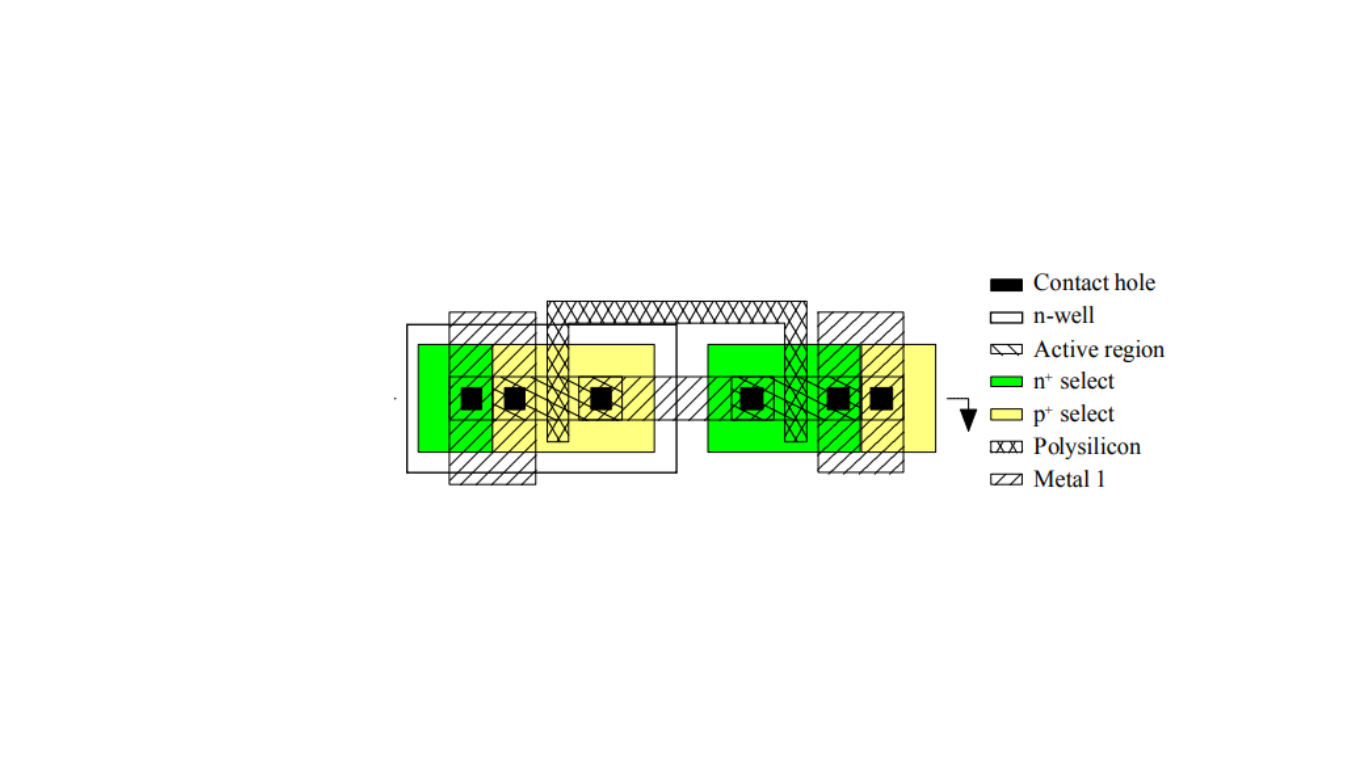

Composite layouts refer to the combination of multiple masks used in the semiconductor fabrication process to create integrated circuits. The process involves using various masks to define different features and regions on the semiconductor wafer.

An active region mask is initially used to define the dimensions of the transistors. This mask specifies where the diffusion (i.e., source and drain regions) will take place.

A select mask is then used for the actual doping process. The openings in the select mask extend beyond the active regions, ensuring that the transistors are formed correctly.

The resulting composite layout includes the active region, select, and other necessary masks to accurately define the structure of transistors during the semiconductor manufacturing process.

The concept of composite layouts allows designers to work more conveniently with the dimensions of transistor source/drain regions while abstracting away the complexities of individual masks. Symbolic layout styles, such as the one mentioned in the context, enable designers to specify transistor properties like active regions and gates. The composite layout is then automatically generated based on these specifications and design rules.