D Flip Flop Truth Tabel

| D | Clock | Q (Output) |

|---|---|---|

| 0 | 0 | Q |

| 1 | 0 | Q |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

In the VLSI design always recommended using a D flip-flop to design the sequential circuits. The main reason behind that is that the main advantage of the D flip-flop is the minimum combinational logic in the data path to get the next state. Designers need to control single D input to get the desired output.

D Flip Flop Using MUX, In digital electronics, a flip-flop is a fundamental building block used to store and manipulate binary data. One commonly used flip-flop is the D flip-flop, which stores a single bit of information and has a clock input to control when the data is stored. In this article, we will explore how to design a D flip-flop using multiplexers, which are versatile digital components that can be used for various purposes, including logic circuit design.

Understanding the D Flip-flop Before we dive into the design, let’s briefly review the functionality of a D flip-flop. A D flip-flop has two inputs: the D (data) input and the clock input. The D input represents the data to be stored, and the clock input determines when the data is latched and stored.

On the rising edge of the clock signal, the D input is sampled, and its value becomes the output of the flip-flop. This output remains unchanged until the next clock edge when it is updated with the new value of the D input. To design a D flip-flop using multiplexers, we can make use of the fact that a multiplexer can function as a combinational circuit with multiple inputs and select inputs. By appropriately connecting the inputs and the select input, we can create a circuit that emulates the behavior of a D flip-flop.

D flip-flop using muxHere’s a step-by-step guide to designing a D flip-flop using multiplexers: Start by considering the truth table of a D flip-flop. The truth table shows the relationship between the D input, the clock input, and the flip-flop outputs. For a D flip-flop, the output is the same as the D input when the clock input is high (1), and it holds its previous state when the clock input is low (0).

Understanding the D Flip-flop Before we dive into the design, let’s briefly review the functionality of a D flip-flop. A D flip-flop has two inputs: the D (data) input and the clock input. The D input represents the data to be stored, and the clock input determines when the data is latched and stored.

On the rising edge of the clock signal, the D input is sampled, and its value becomes the output of the flip-flop. This output remains unchanged until the next clock edge when it is updated with the new value of the D input. To design a D flip-flop using multiplexers, we can make use of the fact that a multiplexer can function as a combinational circuit with multiple inputs and select inputs. By appropriately connecting the inputs and the select input, we can create a circuit that emulates the behavior of a D flip-flop.

D flip-flop using muxHere’s a step-by-step guide to designing a D flip-flop using multiplexers: Start by considering the truth table of a D flip-flop. The truth table shows the relationship between the D input, the clock input, and the flip-flop outputs. For a D flip-flop, the output is the same as the D input when the clock input is high (1), and it holds its previous state when the clock input is low (0).

Here’s a step-by-step guide to designing a D flip-flop using multiplexers:

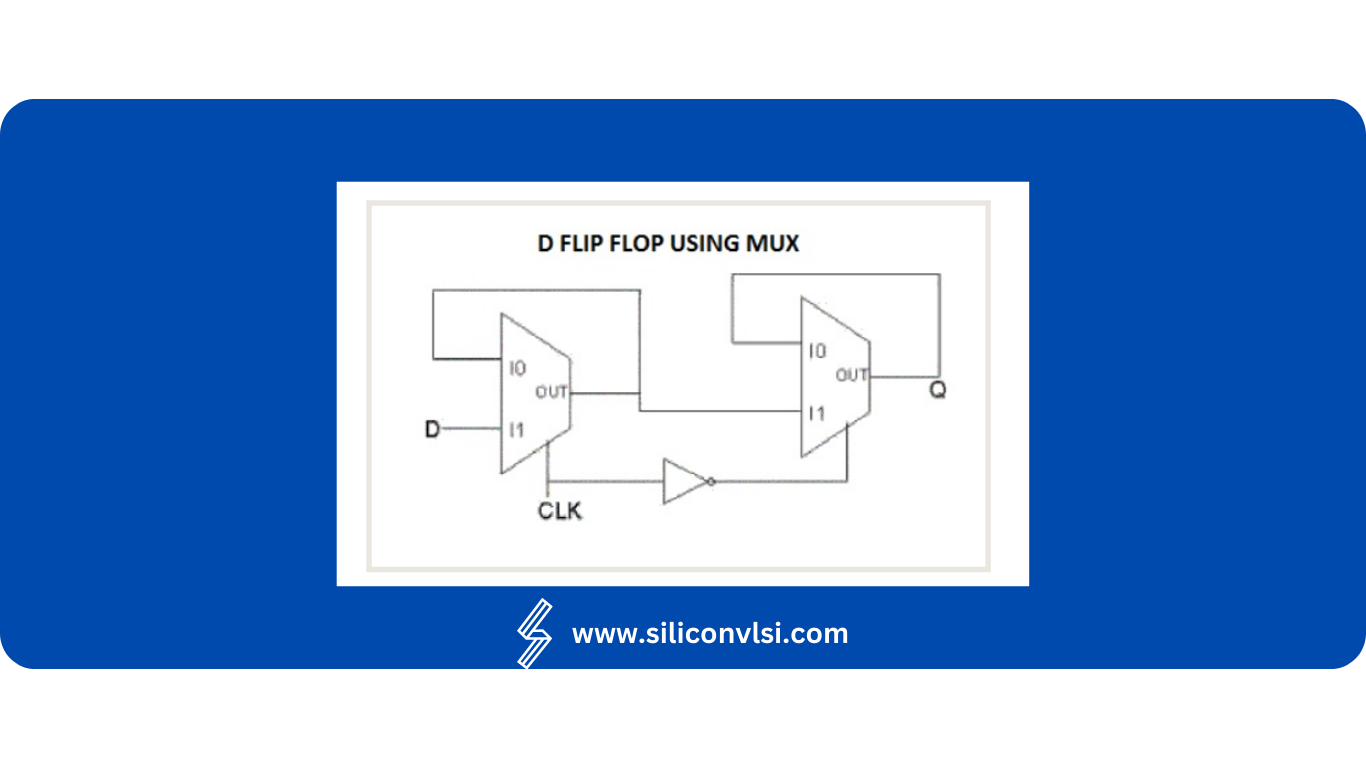

1. As shown in the above figure, We will need two 2:1 multiplexers for our design. Connect the D input to both multiplexers’ input 0, and connect the output of one multiplexer to the input 1 of the other multiplexer. This creates a feedback loop between the two multiplexers.

2. Connect the clock input to the selected input of both multiplexers. This ensures that the clock signal controls the selection of inputs in the multiplexers.

3. Connect the outputs of the multiplexers to form the Q (output) of the flip-flop. This output represents the stored value of the D input.

4. The design of a D flip-flop using multiplexers relies on the ability of the multiplexers to select the appropriate input based on the value of the selected input. When the clock input is high (1), the multiplexers select the D input as the output, which means the output follows the value of the D input. When the clock input is low (0), the multiplexers select their own outputs as the output of the flip-flop, which means the stored value is maintained.

Understanding the Design Designing a D flip-flop using multiplexers is an efficient way to implement this fundamental building block of digital electronics. By leveraging the versatility of multiplexers, we can create a circuit that stores and updates binary data

Use of D Flip Flop

The D flip-flop, also known as a data flip-flop or DFF is a fundamental component in digital logic circuits. It is widely used in sequential circuits for storing and synchronizing data. Here are some of the main uses of a D flip-flop

Data Storage: The primary purpose of a D flip-flop is to store a single bit of data. It has two inputs: a data input (D) and a clock input (CLK). When the clock signal transitions from low to high (rising edge or positive edge), the value at the data input is transferred to the flip-flop’s output, which retains its state until the next clock transition.

Registers and Memory Elements: D flip-flops are essential building blocks for constructing registers and memory elements. By connecting multiple D flip-flops in a chain, it is possible to create larger storage units capable of storing multiple bits of data. These units are widely used in microprocessors, digital systems, and memory devices.

State Holding in Finite State Machines: Finite state machines (FSMs) are commonly used in digital systems to control sequential operations. D flip-flops are important components in FSMs as they hold the current state and enable the transition to the next state based on specific conditions or inputs.

Clock Division and Frequency Division: D flip-flops can be used to divide the frequency of a clock signal. By connecting the output of a flip-flop to its own clock input (feedback), each flip-flop in the chain divides the frequency by 2. This technique, known as frequency division, is useful in various applications such as generating slower clock signals or controlling timing in sequential circuits.

Synchronization and Edge Detection: D flip-flops are commonly used for signal synchronization and edge detection purposes. By using the rising or falling edge of a clock signal to trigger the transfer of data, D flip-flops ensure that the output reflects the input signal at a specific moment in time. This is important when dealing with asynchronous signals or signals with different timings.

Delay Circuit: D flip-flops can be used to introduce a controlled delay in a digital circuit. By connecting the output of a flip-flop back to its input, the output will change only after a specific number of clock cycles. This technique is often used for synchronization or to align signals with different propagation delays.

Shift Registers: D flip-flops can be connected in a serial chain to create shift registers. Shift registers allow the movement of data in a specific direction (shift left or shift right) with each clock pulse. They are used in applications such as data storage, data transmission, and parallel-to-serial or serial-to-parallel conversion.