The Difference Between Flip Flop and Latch

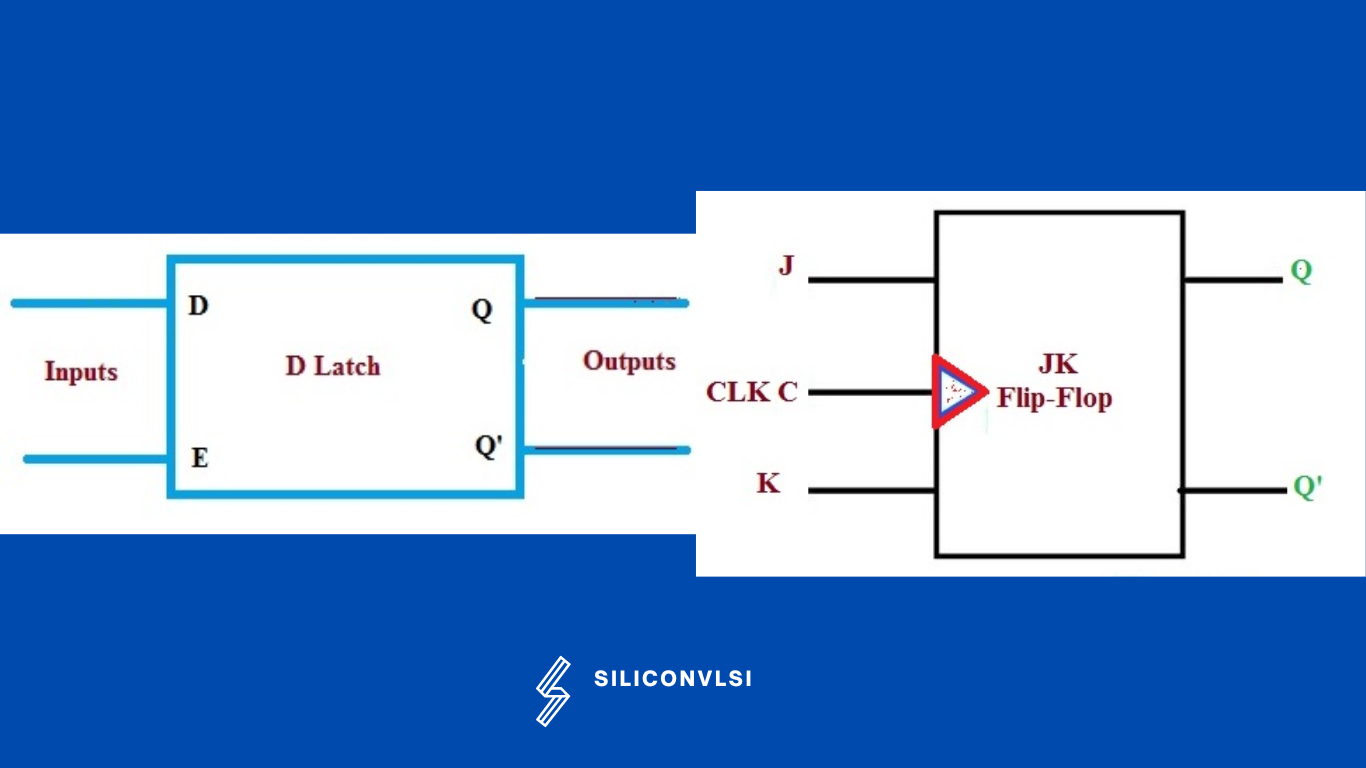

What is a Latch?

A latch is a device that has two stable states namely high output as well as low-output and includes a feedback lane also latch is a memory device used to store one bit of data. These are the same as flip-flops, but they are not synchronous devices and They do not work on the edges of the clock as Flip-flop

What is a Flip-Flop?

A Flip-Flop is a couple of latches, and the designing of this can be done using a NOR gate or a NAND gate. so it has 2 inputs, 2 outputs, a set as well a reset. it’s used to store the binary values. A Flip-Flop will have an extra CLK signal to make it work in a different way as compared to the latch.

Difference between Latches and Flip-Flops

The main distinction between a flip-flop and a latch is their triggering mechanism. A flip-flop is edge-triggered, whereas a latch is level-triggered. In practical terms, this means that the output of a latch changes whenever there is a change in the input signal.

| No. | Flip-flop | Latch |

|---|---|---|

| 1 | Flip-flop has two stable states that are represented as 0 and 1. also called a bistable device | The latch is also a bistable device whose states are also represented as 0 and 1. |

| 2 | It is an edge-triggered device. | It is a level-triggered device. |

| 3 | A flip-flop can be clocked for all time | A Latch may be clockless or clocked |

| 4 | Gates like NOR, NOT, AND, and NAND are building blocks of flip-flops. | These are also made up of gates. |

| 5 | They are classified into asynchronous or synchronous flip-flops. | There is no such classification in latches. |

| 6 | It forms the building blocks of many sequential circuits like counters. | These can be used for the designing of sequential circuits but are not generally preferred. |

| 7 | Flip-flops always have a clock signal | The latch doesn’t have a clock signal |

| 8 | Flip-flops can be built from Latches | Latches can be built from gates |

| 9 | Example: D Flip-flop, JK Flip-flop # | Example: SR Latch, D Latch |