Dynamic IR drop occurs when the inputs of a circuit are continuously switching, indicating that the circuit is in a functional state. In this dynamic stage

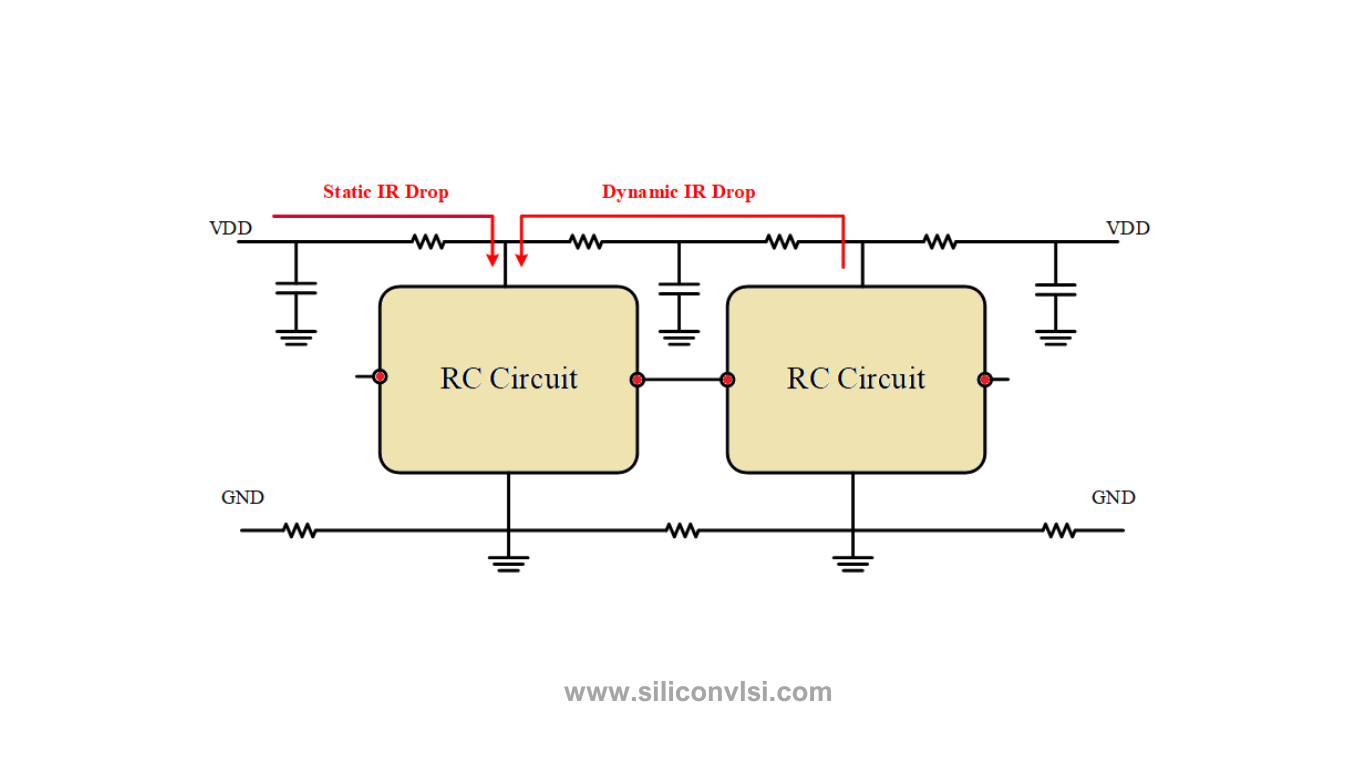

The static IR drop refers to the voltage drop that transpires in the PDN when the circuit is in a static stage, indicating that there are no inputs switching. In this state, the circuit remains inactive, and its components are in a stable state. However, even during this idle period, there can be a certain degree of voltage drop within the power delivery network.

On the other hand, Dynamic IR drop occurs when the inputs of a circuit are continuously switching, indicating that the circuit is in a functional state. In this dynamic stage, the components of the circuit are actively processing data, executing instructions, or performing calculations. Consequently, the current flowing through the instance.

How to improve Dynamic IR Drop

Optimize Power Delivery Network Design

A well-designed power delivery network forms the foundation for mitigating dynamic IR drop. Consider the following strategies:

a) Decoupling Capacitors: Incorporate an appropriate number of decoupling capacitors within the PDN. These capacitors act as local energy reservoirs, absorbing the dynamic current demands and minimizing voltage fluctuations.

b) Power Grid Distribution: Optimize the power grid distribution by ensuring adequate power and ground plane connectivity, reducing resistance and inductance in the PDN.

c) Routing Considerations: Carefully route power and ground traces, minimizing their length and avoiding sharp turns or congested areas to minimize resistance and parasitic effects.

Current Distribution Analysis

Perform a thorough current distribution analysis to identify potential areas of excessive current density. By identifying these “hotspots,” engineers can take targeted measures to redistribute the current and reduce the likelihood of significant dynamic IR drop.

Clock Tree Optimization

The clock tree plays a vital role in circuit operation, and its design can impact dynamic IR drop. Optimize the clock tree by considering the following:

a) Buffer Insertion: Insert buffer stages strategically within the clock tree to balance the load and minimize voltage droop.

b) Clock Skew Management: Manage clock skew to ensure uniform switching rates throughout the circuit, preventing localized areas of excessive current and mitigating dynamic IR drop.

Switching Activity Reduction

Reducing the overall switching activity in the circuit can effectively alleviate dynamic IR drop. Consider implementing the following measures:

a) Clock Gating: Utilize clock gating techniques to disable clock signals in idle or inactive regions, reducing unnecessary switching activity and associated current demand.

b) Power Gating: Employ power gating methods to selectively disable power supply to inactive circuit blocks, minimizing dynamic IR drop and conserving power.