Intermetal Low-k Dielectrics

Low-k Characteristics

Reducing the interline capacitance is important for the ongoing scaling of on-chip interconnects. The capacitance between neighboring metal wires is composed of three components: an area component, a fringing field component, and a wire-to-wire capacitance component [3]. To decrease the capacitance, the prevalent solution is to replace chemical vapor deposition (CVD) deposited silicon oxide with low-k materials in the intermetal dielectric stack. CVD silicon oxide, with a k value of around 4.2, serves as the reference material for low-k dielectrics.

Currently, there are mainly two approaches to reducing the k value of dielectric films:

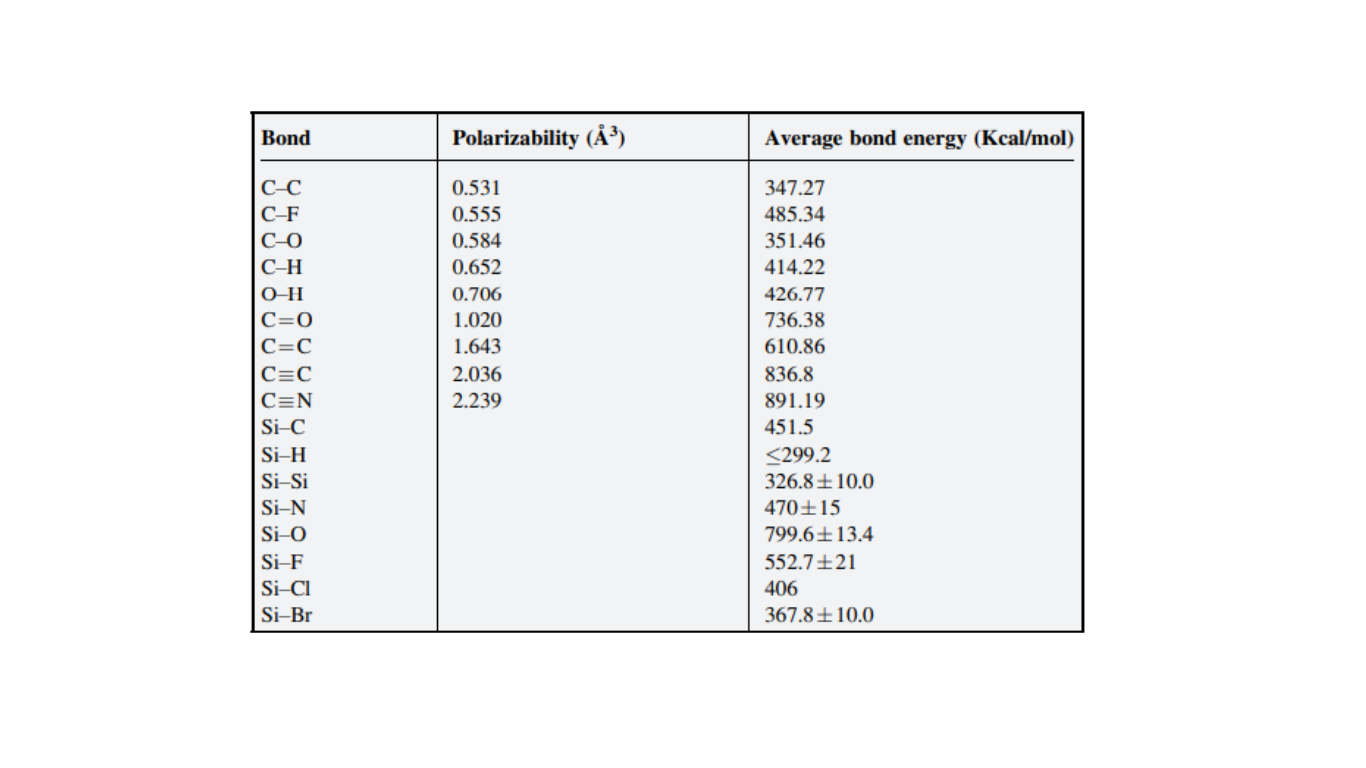

1. Material Composition Modification: This approach involves altering the composition of the dielectric material to reduce its dielectric constant. By introducing elements or compounds with lower polarizability, the overall k value of the material is decreased.

2. Porosity Introduction: Creating a porous structure within the dielectric material can significantly reduce the effective dielectric constant. The introduction of voids or pores reduces the amount of material that interacts with the electric field, leading to a lower overall k value.

In summary, intermetal low-k dielectrics play a critical role in reducing interline capacitance for on-chip interconnect scaling. The selection of low-k materials and their properties is essential for achieving the desired performance while considering trade-offs between dielectric constant reduction and maintaining thermal, mechanical, and electrical characteristics. Material composition modification and porosity introduction are two common approaches to achieving lower k values in dielectric films.

Why Low-k Matters

The key property of a dielectric is its dielectric constant, often shown as the letter k. As you and I may already know, traditional materials like silicon dioxide have a k-value around 4. But if we want to reduce capacitance—which directly impacts signal delay and power consumption—we need to look for materials with an even lower k-value. That’s exactly why low-k dielectrics are so important.

When we talk about “intermetal low-k dielectrics,” we’re referring to these specially engineered insulating materials that you and I place between metal interconnects in integrated circuits. Using them helps us achieve faster signal speeds and lower power usage—something every chip designer aims for.