Macro Cell

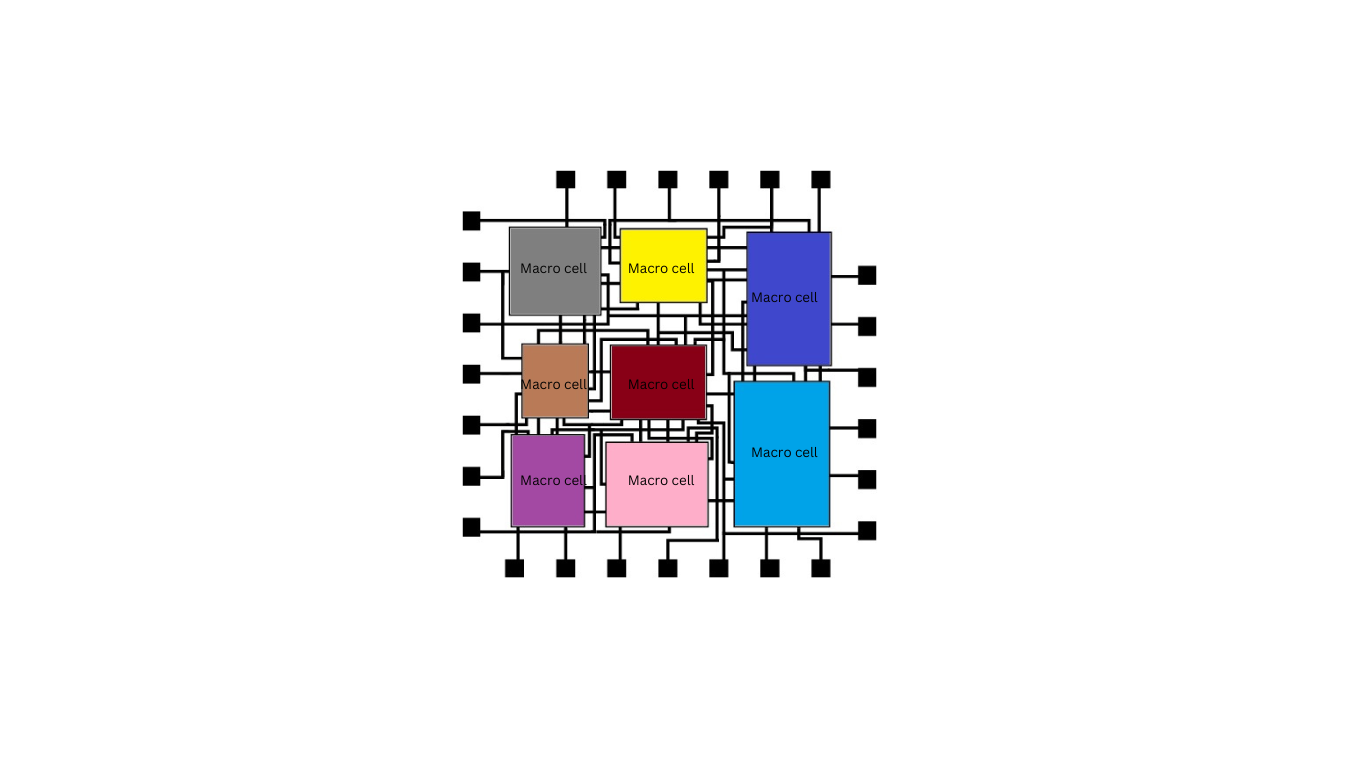

The term “macro cell” or “mega cell” in the context of ASICs signifies a predefined block that exhibits a significantly higher level of complexity compared to standard cells. These macro cells are essentially intellectual properties (IP) that can be incorporated into an ASIC design. Macro cells are used to implement complex functions within an ASIC and offer several advantages and challenges:

Examples of Macro Cells

Macro cells can encompass a wide range of functions, including but not limited to:

- RAM cells

- ROM cells

- Serial interfaces

- Timers

- Arithmetic Logic Units (ALUs)

- Processor cores

Characteristics of Macro Cells

Higher Complexity: Macro cells are designed to handle complex and specialized functions, making them larger and more intricate than standard cells.

Flexible Form: Unlike standard cells, macro cells do not adhere to a strict row structure. They can be placed within the ASIC layout as needed.

Specific Masks: Each macro cell is created as a unique block with its specific layout, requiring dedicated masks for fabrication.

Types of Macro Cells

Hard Macro: A hard macro has a fixed layout and is described by a simulation that includes layout-related influences. It essentially functions as a pre-built and well-characterized block that can be placed directly into an ASIC design. Embedding a hard macro is akin to placing a physical component.

Soft Macro: In contrast, a soft macro is typically defined by a netlist or VHDL code, representing the logical functionality of the cell. However, layout and simulation data must still be generated to integrate the soft macro into the ASIC design. Soft macros offer more flexibility in terms of customization.

Advantages of Macro Cell Design Style

Fast Design: Incorporating macro cells into an ASIC design can significantly expedite the design process, as complex functions are pre-designed and validated.

Short Time to Market: The use of macro cells reduces development time, enabling faster product launches.

Economical for Medium Complexity: Macro cell-based design strikes a balance between design effort and cost-effectiveness and is particularly economical for ASICs with moderate complexity.

Low Design Risk: Since macro cells are pre-designed and tested, they reduce design risk by providing reliable and proven functionality.

Disadvantages of Macro Cell Design Style

Effort for Integration: While macro cells offer pre-designed functions, integrating them into an individual ASIC design may still demand a certain level of effort, especially for customization and connectivity.

Cost of IPs: Acquiring macro cells or IPs can come at a price, and the cost may be significant for some specialized functions.

Inefficiency for Small-Scale Production: Macro cell-based design may not be cost-effective for ASIC projects with a small number of parts, as specific masks must be produced for each chip, potentially leading to higher per-unit costs.

In summary, the macro cell design style in ASICs is a valuable approach for implementing complex and specialized functions efficiently. It reduces design time, lowers design risk, and is economically viable for medium-complexity ASICs. However, it may involve additional costs for acquiring IPs, and it may not be efficient for small-scale production runs due to the mask costs associated with each ASIC