Master-Slave D Flip-Flop: Positive or Negative Edge-Triggered?

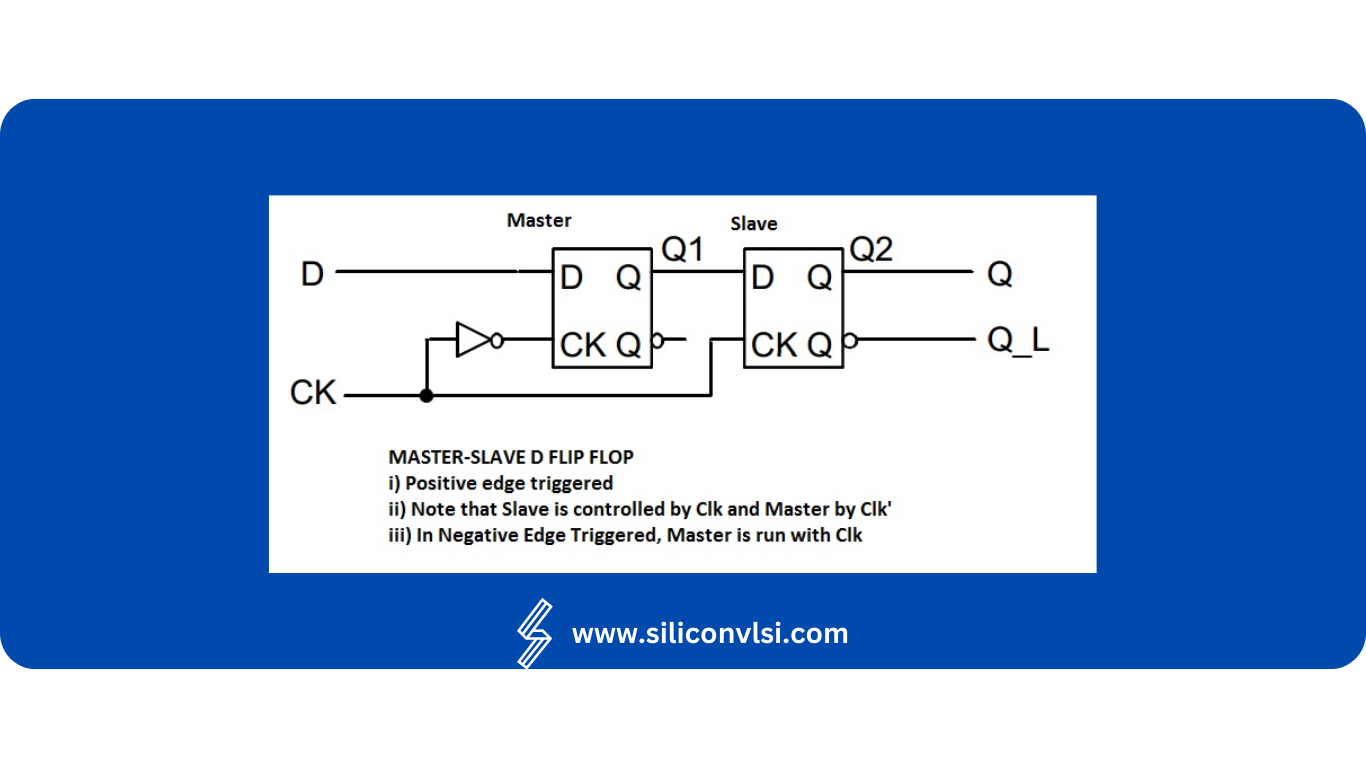

In digital electronics, you can use a master-slave D flip-flop to store and transfer data. It consists of two interconnected D flip-flops, which we refer to as the master and the slave. The behavior of a master-slave D flip-flop is triggered by either the positive edge or the negative edge of a clock signal. In this explanation, we will explore the characteristics of both positive edge-triggered and negative edge-triggered master-slave D flip-flops so you can understand their differences and applications.

Positive Edge-Triggered Master-Slave D Flip-Flop

In a positive edge-triggered master-slave D flip-flop, the transfer of data occurs on the rising edge of the clock signal. When the clock signal transitions from low (0) to high (1), the master flip-flop captures the input data. The captured data is then transferred to the slave flip-flop on the next rising edge of the clock signal. This ensures that the output of the flip-flop reflects the value of the D (data) input at the moment of the rising edge. The positive edge-triggered master-slave D flip-flop is commonly used in synchronous digital systems.

Negative Edge-Triggered Master-Slave D Flip-Flop

In contrast, a negative edge-triggered master-slave D flip-flop transfers data on the falling edge of the clock signal. When the clock signal transitions from high (1) to low (0), the master flip-flop captures the input data. The captured data is then transferred to the slave flip-flop on the next falling edge of the clock signal. This ensures that the output of the flip-flop reflects the value of the D input at the moment of the falling edge. The negative edge-triggered master-slave D flip-flop is also commonly used in synchronous digital systems.

Choosing between Positive and Negative Edge-Triggered Flip-Flops

The choice between a positive edge-triggered and a negative edge-triggered master-slave D flip-flop depends on the specific requirements of the digital system being designed. Here are some considerations:

Clock Signal Characteristics: The decision may depend on the characteristics of the clock signal available in the system. If the clock signal has a stronger and more reliable rising edge, a positive edge-triggered flip-flop may be preferred. Conversely, if the falling edge of the clock signal is more stable and accurate, a negative edge-triggered flip-flop may be chosen.

Propagation Delay: Another factor to consider is the propagation delay in the flip-flop circuit. Positive edge-triggered flip-flops tend to have shorter propagation delays since the data transfer occurs immediately after the rising edge. However, negative edge-triggered flip-flops can be advantageous when dealing with specific timing constraints in the system.

Design Constraints: The design constraints of the digital system, such as power consumption, noise immunity, and overall performance, may influence the choice of flip-flop type. Positive edge-triggered flip-flops are generally more commonly used and widely available, which may make them a more convenient choice in many cases.

Use of Master-Slave D Flip-Flops

In digital electronics, master-slave D flip-flops play a important role in various applications where data storage and synchronization are required. These flip-flops provide a reliable and efficient means of storing and transferring data based on clock signals. In this article, we will explore some common uses of master-slave D flip-flops and how they contribute to the functionality of digital systems.

Synchronous Systems One of the primary applications of master-slave D flip-flops is in synchronous digital systems. In such systems, all components operate based on a central clock signal, ensuring that data transfers and operations are synchronized. Master-slave D flip-flops enable the synchronization of data with the clock signal, ensuring that the output reflects the value of the input at a specific clock edge.

Clock Domain Crossing Another important application is clock domain crossing. In digital systems with multiple clock domains, where different components operate at different clock frequencies, master-slave D flip-flops are used to safely transfer data between these clock domains. The master-slave structure ensures that the data is synchronized with the destination clock domain, preventing issues such as metastability.

Register and Memory Elements Master-slave D flip-flops are commonly used as basic building blocks for constructing larger register and memory elements. Registers are sequential circuits that store multiple bits of data, and memories are arrays of registers that store larger amounts of data. By cascading multiple master-slave D flip-flops together, designers can create registers and memories of various sizes to meet the needs of the digital system.

Registers are essential for temporary data storage, holding intermediate results during computations or acting as storage for data processing operations. Memories, on the other hand, provide long-term storage capabilities, allowing data to be retained even when the power is turned off. The use of master-slave D flip-flops in these elements ensures reliable data storage and retrieval.

State Machines and Control Logic State machines are commonly used in digital systems to implement control logic, sequencing through different states based on inputs and a clock signal. Master-slave D flip-flops are often used within state machines to store and update the current state information. Each flip-flop represents a specific state, and the outputs of the flip-flops determine the system’s behavior.

By utilizing the master-slave structure, state machines can be designed to transition to the next state only at specific clock edges, ensuring proper synchronization. This allows for precise control of the system’s operation, enabling complex functionalities in areas such as digital control systems, communication protocols, and sequential data processing.

Master-slave D flip-flops serve as vital components in digital systems, enabling reliable data storage, synchronization, and control. Their use in synchronous systems, clock domain crossing, registers, memories, and state machines highlights their versatility and importance. Understanding the applications of master-slave D flip-flops empowers designers to utilize these components effectively in their digital system designs, ensuring proper data handling and system functionality.

Conclusion Both positive edge-triggered and negative edge-triggered master-slave D flip-flops are widely used in digital systems. The selection between these two types depends on the specific requirements of the system, including the characteristics of the clock signal, propagation delay considerations, and design constraints. Understanding the differences and applications of each type will enable designers to make an informed decision when implementing master-slave D flip-flops in their circuits.