Device reliability is a crucial aspect of CMOS technology, and factors like smaller device dimensions and the use of new materials impact CMOS device reliability significantly. As integration scales up, each circuit element faces stricter reliability requirements. However, testing complex circuits with low failure rates poses challenges in terms of cost and time.

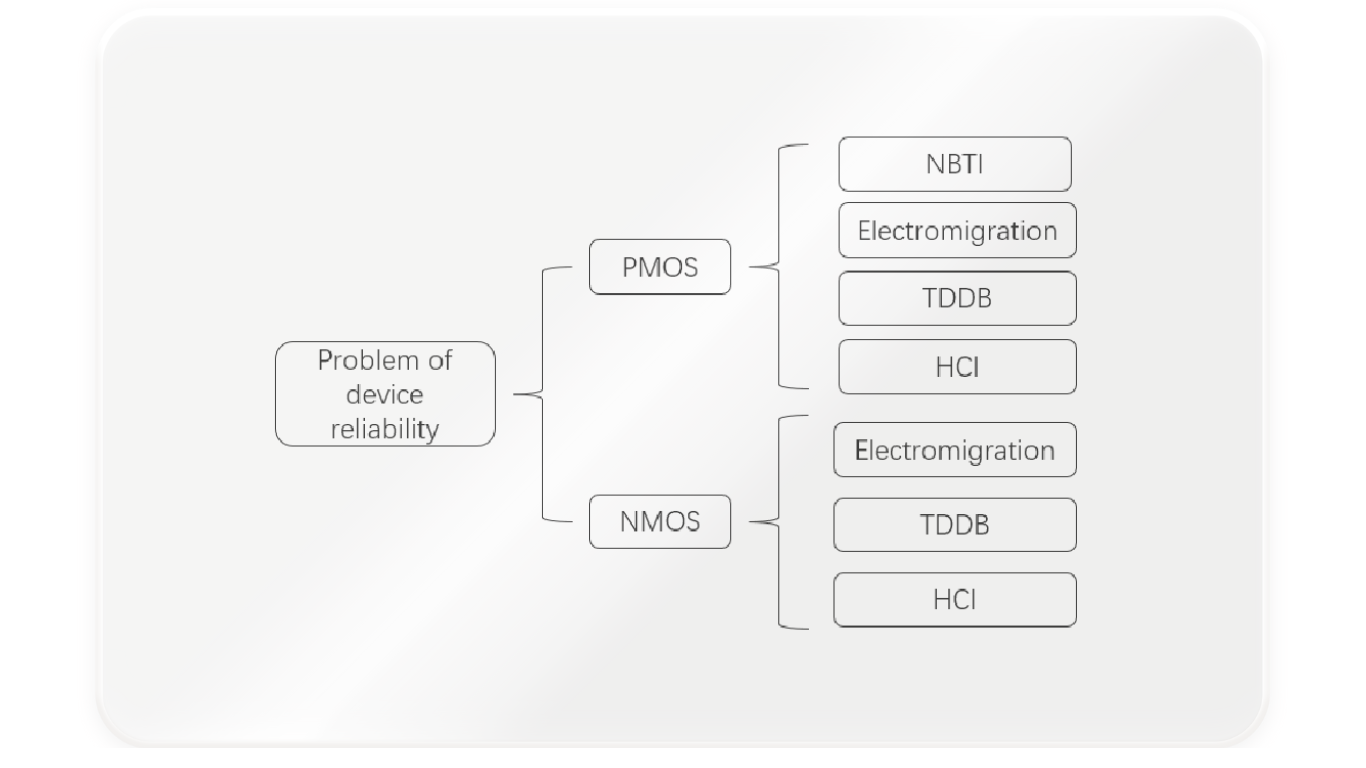

Here’s an overview of some major CMOS reliability concerns related to the front-end process:

Time-Dependent Dielectric Breakdown (TDDB): TDDB of SiO2 has been the subject of extensive research, but a clear conclusion hasn’t been reached. With voltage and thickness scaling, new failure modes like soft breakdown become significant. Predicting low-voltage operation lifetime based on high-voltage accelerated tests is a topic of interest. Researchers are also exploring the reliability limits of scaling SiO2 gate dielectrics. Some believe that with improved uniformity, SiO2 gate dielectric scaling to below 20 Å is feasible. For high-κ gate dielectrics, TDDB reliability is less studied, and they tend to have smaller bandgaps and higher trap densities, affecting TDDB.

Hot-Carrier Effects: In normal operation, high lateral electric fields generate hot carriers near the drain side, damaging gate dielectrics and degrading device characteristics. As channel length reduces, the peak electric field increases. Adjusting doping profiles and power supply voltage scaling can mitigate this. While power supply voltage reduction can limit hot-carrier energy gain, other mechanisms explain observed experimental results.

Negative Bias Temperature Instability (NBTI): NBTI is a significant cause of threshold voltage shift in p-MOSFETs. Under NBTI stress, gate bias is negative, leading to positive charge generation in the gate oxide and interface state generation, causing gm degradation and Vth shift. NBTI impacts analog or mixed-signal applications and has a growing impact on digital circuits with technology scaling. Nitridation, used to suppress boron penetration, can reduce p-MOSFET NBTI lifetime. NBTI becomes a limiting factor for circuit lifetime, especially under certain conditions.

In conclusion, CMOS device reliability faces challenges due to smaller dimensions and new materials. Understanding and addressing these challenges through innovative device structures, better uniformity, and robust design methodologies are essential for improved performance and yield.