Why NMOS pass strong 0 and weak 1

We all know that when Vgs > Vt, at that time only Nmos will turn on.

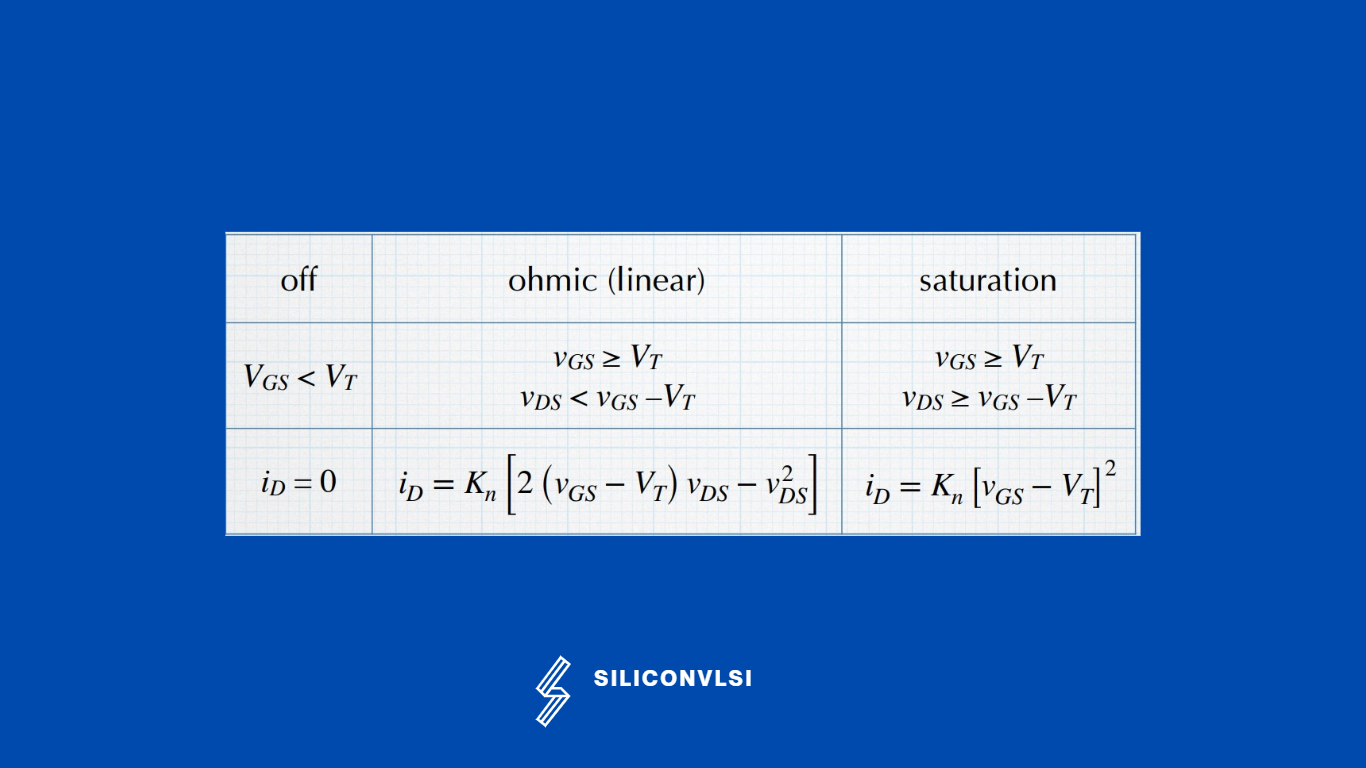

NMOS Current Equation:

Now to understand NMOS pass strong 0 and weak 1, let’s take one example. Suppose we have one NMOS. As shown in the following figure, let’s take Vdd=1v, Vgs=1v, and Threshold voltage(Vt) = 0.2v. And Initially, Capacitor(Vcc) is 0v.

![]()

After Some time, lets assume that capacitor Vcc, Charged by 0.2v, so Vgs = Vg – Vs = 1 – 0.2 = 0.8 > 0.2(vt). So node Vcc charged by 0.2v and still Vgs is greater than Vt. So still current will flow from the drain to the source.

![]()

After Some time, that capacitor Vcc is charged by 0.6v, so Vgs = Vg – Vs = 1 – 0.6= 0.4 > 0.2(vt). So node Vcc charged by 0.6v and still Vgs is greater than Vt. So still current will flow from the drain to the source.

![]()

After Some time,that capacitor Vcc, charged by 0.8v, so Vgs = Vg – Vs = 1 – 0.8= 0.2 = 0.2(vt). So node Vcc charged by 0.8v and still Vgs is equal to Vt. So still current will flow from the drain to the source.

![]()

Now As soon As Vcc becomes 0.8v, after that, it will not charge further because Vgs > Vt, the condition is not satisfying, so at 0.8v only, NMOS will pass, and after that, it will stop charging that capacitor. Based on the above explanation, we can say that NMOS is Weak to pass 1, which means NMOS can not fully charge the capacitor. It will charge up to Vcc = Vdd – Vt.

NMOS Pass Characteristics

![]()

Please comment below if You like this article.