NAND Gate

The circuit diagram of a NAND gate in CMOS logic is shown on the right. When both inputs A and B are high, both the NMOS transistors (bottom half of the diagram) conduct, and neither of the PMOS transistors (top half) conduct. This establishes a conductive path between the output and Vss (ground), causing the output to go low. On the other hand, if either input A or B is low, one of the NMOS transistors will not conduct, one of the PMOS transistors will, and a conductive path will be formed between the output and Vdd (voltage source), resulting in the output going high.

CMOS Advantage

One advantage of CMOS over NMOS is that both low-to-high and high-to-low output transitions are fast. This is because the pull-up transistors have low resistance when switched on, unlike the load resistors in NMOS logic. Additionally, the output signal swings the full voltage between the low and high rails, making it a strong and more symmetric response. This feature also enhances CMOS’s resistance to noise. For calculating delay in a CMOS circuit, the Logical effort method can be used.

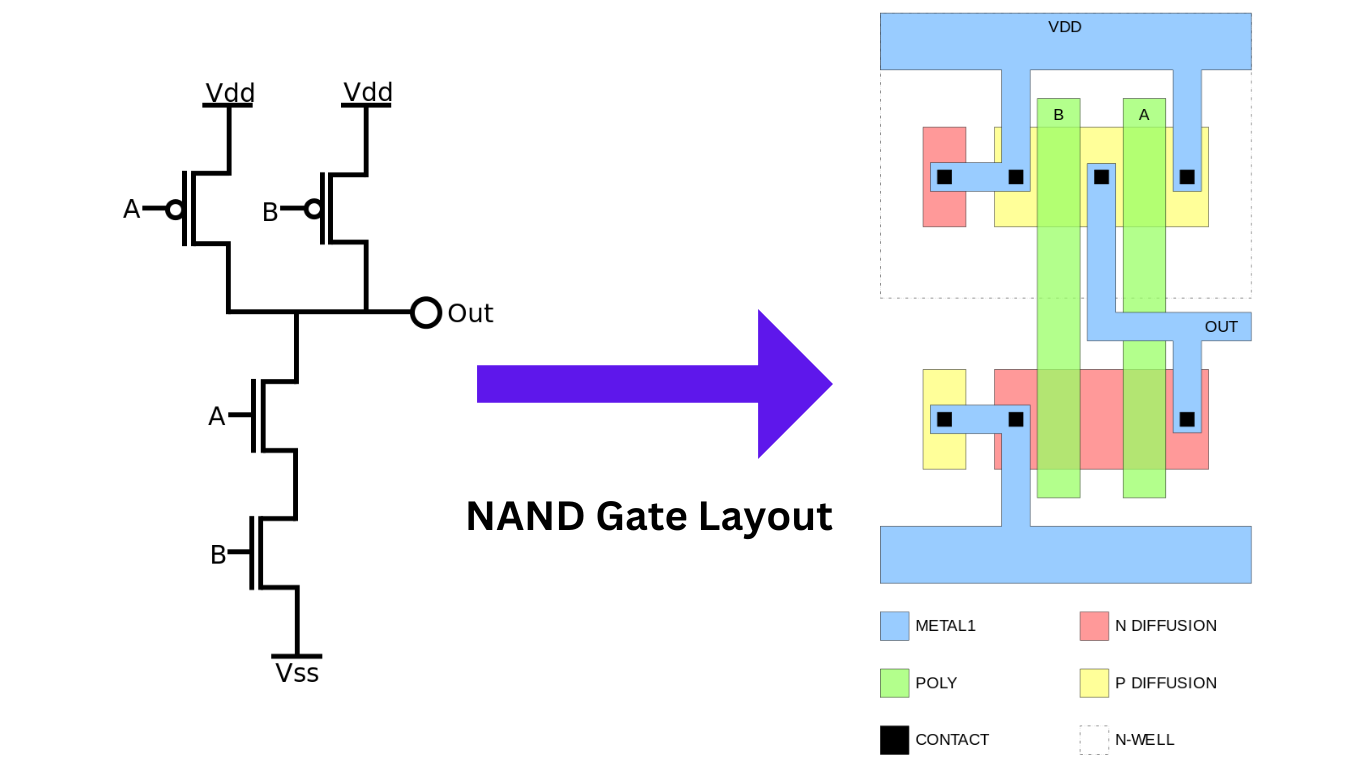

NAND Gate Layout

This illustration depicts a NAND logic device, presented as a physical representation reflecting its manufacturing process. The layout provides a top-down view of stacked layers, resembling a “bird’s eye view.” The circuit is constructed on a P-type substrate.

The essential layers, namely polysilicon, diffusion, and n-well, are referred to as “base layers” and are inserted into trenches within the P-type substrate. The contacts establish connections by penetrating an insulating layer between the base layers and the first layer of metal (metal1).

The inputs to the NAND (highlighted in green) are in polysilicon. The CMOS transistors (devices) are formed at the intersection of the polysilicon and diffusion: N diffusion for the N device, and P diffusion for the P device, distinguished by salmon and yellow coloring, respectively. The output (“out”) is connected together in metal, represented in cyan coloring. Connections between metal, polysilicon, or diffusion are established through contacts depicted as black squares. Notably, this physical layout example aligns with the NAND logic circuit presented in the previous example.

The N device is manufactured on a P-type substrate, while the P device is created within an N-type well (n-well). To prevent latch-up, a P-type substrate “tap” is connected to VSS, and an N-type n-well tap is connected to VDD.