Standard Cell Library

The standard cell library is a collection of standard logic gates that are used to design a full chip. A standard cell library is a collection of well-defined and appropriately characterized logic gates that can be used to implement a digital design. The standard cells are much like the biological cells in our bodies, which are the basic building blocks. The cells provide the basic logic functions, such as, NOT, AND, OR, NAND, NOR, XOR, flip-flop, buffer, etc.

Standard Cell Library Data

A standard cell library contains two main components:

Timing information: This is typically in the Synopsys Liberty format and provides functional definitions, timing, power, and noise information for each cell.

Layout information: Typically in LEF format, which contains reduced information about the cell layouts, required by the automated ‘Place and Route’ tools.

Cell library also contains the following information

- The complete layout of the cells

- SPICE model or netlist of the cells

- Verilog or VHDL model of the cells

- Reliability models of the cells

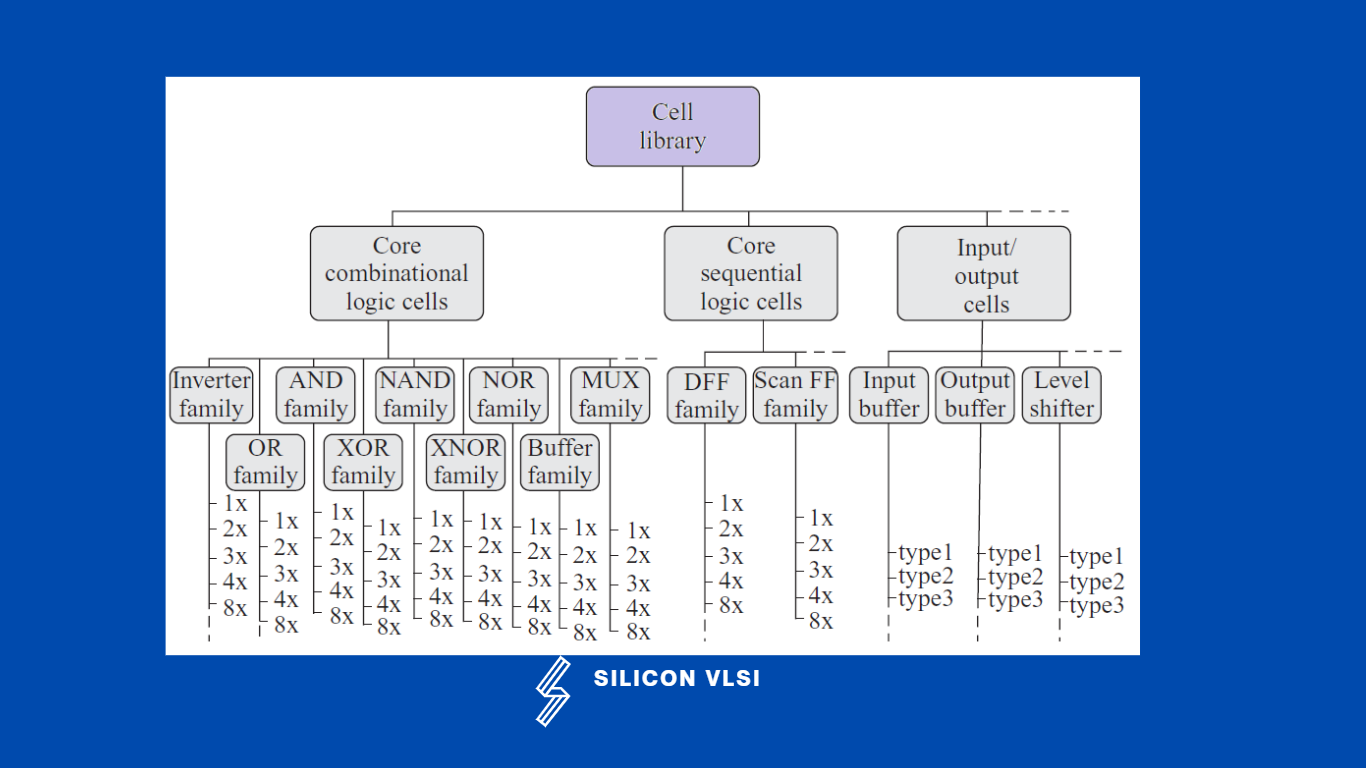

The following figure shows the contents of a typical standard cell library. First, a basic set of standard cells is designed for a given process technology node and these cells are characterized to evaluate their properties, such as area, speed, and power dissipation. These basic cells are packed to form a prototype cell library, and then are used to design a prototype full-chip, and requirement criteria are measured. If the requirements are met, the process technology qualifies for production.

The prototype cell library is so called because it is a very quickly designed cell library that just contains a few basic cells, which are functionally verified, and only timing and power characterization are done. But no other verifications, such as design rule checking, and reliability checking are not performed. Once the cell library qualifies the customer requirements in terms of area, speed, and power, the cell library is designed to contain all the required cells, characterized and verified.

The standard cell library contains the following two types of cells

Core Cells

These are the basic cells that provide logical operations, such as AND, OR, NOT, and so on. These are called core cells as they form the core of the full chip. The cells that are used to design the logic of the circuit are known as core cells. Core cell’s specific characteristics. #

- They are of fixed height.

- They have a variable width.

- Standard cells are placed in rows.

- They are designed to end on the left and right sides.

- Interconnects are routed in channels placed between standard cell rows.

Input/Output Cells

The I/O cells do not have any functional requirements. They act as the interface between the internal core logic and the outside of the chip. The cells that are used to interface the core logic and the external world are called I/O cells. They are placed between the bond pads and core cells at the boundary of the die. #

Standard Cell Library Characterization.

Cell library characterization is a process of analyzing a circuit using static and dynamic methods to generate models suitable for chip implementation flows. #

Cell Library Characterization Output.

- Delay

- Tristate

- Glitch Power

- Setup Time

- Hold Time

- Recovery Time

- Removal Time

- Leakage Power #

- Hidden Power

- Transition Time

- Dynamic Power

- Input Capacitance

- Gate Leakage Current

- Leakage Current

- Ground Waveforms

- Minimum Pulse Width

- Output Current Waveform

- Input Receiver Capacitance

- Power Supply Waveforms