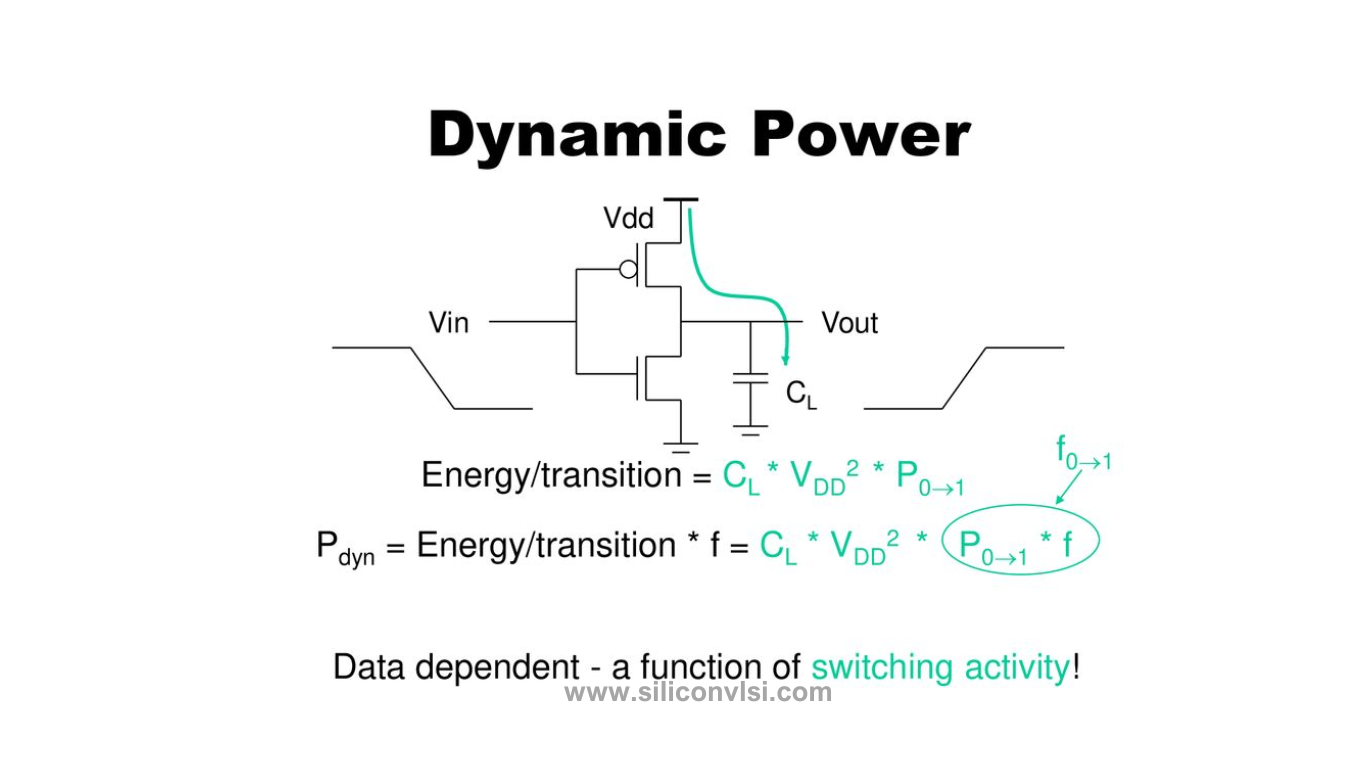

Dynamic power is the energy your digital circuit consumes while actively operating or transitioning between logic states. It comes from switching activities like charging and discharging capacitances and the currents flowing through transistors. Whenever we deal with active circuits, managing dynamic power is crucial to ensure efficiency and reliability.

In a digital circuit, dynamic power consumption occurs due to two main components:

Charging and Discharging Capacitances: When digital signal transitions from one logic state to another, the capacitive components within the circuit, such as the gate capacitance of transistors and interconnect capacitances, need to be charged or discharged. This charging and discharging process requires energy, and as a result, power is consumed. The amount of power consumed depends on factors such as the capacitance being switched, the voltage levels, and the frequency of switching.

Current Flow through Transistors: During switching, as transistors change their states, there is a transient period where both the PMOS (p-channel metal-oxide-semiconductor) and NMOS (n-channel metal-oxide-semiconductor) transistors may momentarily conduct current simultaneously. This situation creates a direct current path between the power supply and the ground, resulting in a brief period of power consumption.

Dynamic power consumption is a significant component of the total power consumed by digital circuits, especially in high-performance designs and applications. Reducing dynamic power is important for improving energy efficiency and minimizing power-related challenges such as excessive heat dissipation and limited battery life.

Design techniques to manage dynamic power consumption include:

Clock Gating: By selectively disabling clock signals to unused or idle circuit portions, clock gating reduces unnecessary switching activities, resulting in power savings.

Voltage Scaling: Adjusting the supply voltage to an optimal level based on the operating conditions can help reduce dynamic power consumption. Techniques like dynamic voltage scaling (DVS) or adaptive voltage scaling (AVS) match the voltage level to the required performance, allowing for power savings.

Power Gating: Completely shutting off the power supply to inactive or idle circuit blocks using power gating techniques conserves power. This technique is commonly employed in low-power designs to minimize leakage power.

Logic Optimization: Optimizing the circuit design, such as reducing the switching capacitance, optimizing gate-level structures, and employing efficient coding styles, can help decrease dynamic power consumption.

By employing a combination of these techniques, designers can effectively manage dynamic power consumption and achieve better energy efficiency in digital circuit designs.