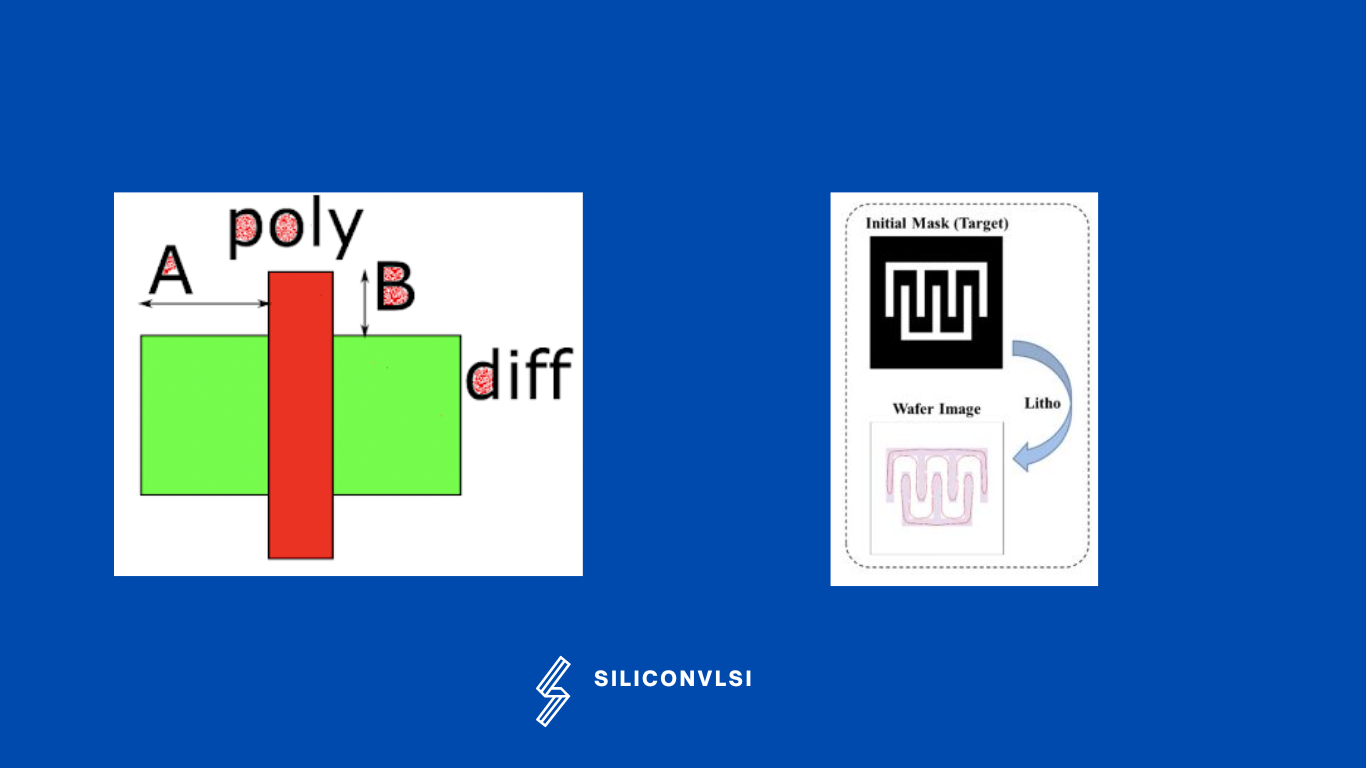

We extend Poly from the diffusion to avoid the short circuit between the source and drain during fabrication.

During the fabrication process, there are chances that the mask gets a slight misalignment.

We all know that we can’t get the exact design in fabrication. there is a reduction or shrink factor in the VLSI Fabrication process(around 1~2%).

To avoid this corner layout effect, or to improve this shrink factor, we are using OPC(optical proximity correction) based on virtual edge and mask pixelation with a two-phase sampling.

What is the length of diffusion effect in VLSI?

The Length of Diffusion (LOD) refers to the distance from an n-channel or p-channel to the edge of the shallow trench isolation (STI) oxide. Oxide Diffusion (OD) to OD spacing represents the spacing between active areas, known as active-to-active spacing. These factors are part of layout-dependent effects in semiconductor device design.