What is Drain-Induced Barrier Lowering in MOSFET?

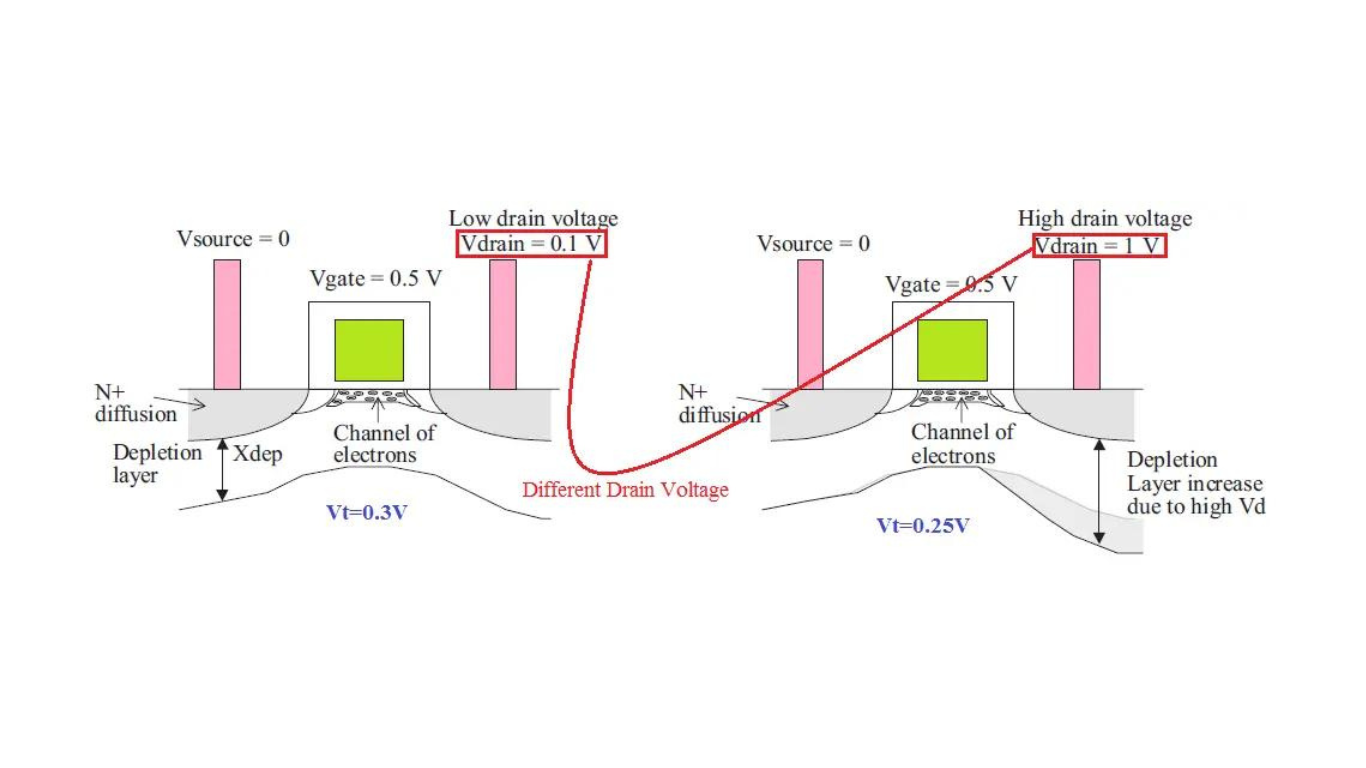

Drain-Induced Barrier Lowering: When we apply a positive voltage to the drain of the Short channel device, threshold voltage(Vt) will be reduced due to the depletion region under the drain region, and overall channel length will reduce, this is called Drain-induced barrier lowering(DIBL).it is also called as short channel effect in CMOS.

When we apply a positive voltage to the drain of a long-channel nMOS device, we observe no significant change in the value of Vt. But When we do the same for a short-channel nMOS device.

The physical origin of DIBL is the increase of the depletion layer due to a high value of Vds that reduces the equivalent channel length and consequently decreases the threshold voltage

Effect of Drain-Induced Barrier Lowering

It causes the reduction of threshold voltage and results in the subthreshold current varying with a higher drain bias called DIBL

List of Short Channel Effects

• Sub-Threshold current

• Vt voltage variation

• Drain-induced barrier lowering

• Drain punch through

• Hot carrier effect

How to reduce or minimize Drain-Induced Barrier Lowering

- Increase substrate doping concentration

- Reduce oxide thickness

- Halo Dopping

Impact of threshold voltage

The threshold voltage of an enhancement-type MOSFET is the minimal gate-to-source voltage required to produce an inversion zone for charge carrier conduction across the device, between the drain and the source, when a proper bias is placed between them.

In a MOSFET, there are two primary methods for lowering the threshold voltage:

Reduction of channel length

Reducing the oxide thickness

Difference between CLM and DIBL in MOSFET?

Channel Length Modulation (CLM) is due to the depletion region shortened channel. Higher VDS results in a shorter effective channel.

Drain-Induced Barrier Lowering (DIBL): due to the depletion region shortened channel, there are fewer mobile charge carriers, hence a smaller gate voltage is enough to balance their electric field. The higher the VDS, the lower the Vth.

What is the DIBL measurement?

The DIBL measures the change of the threshold voltage to the drain voltage.