SRAM Butterfly Architecture

In SRAM memory, butterfly architecture is used to reduce the wordline (WL) line load capacitance. The name “Static Random Access Memory” (SRAM) is derived from its ability to hold data statically as long as it is powered. SRAM is a type of memory that stores a single bit of data (logic 1 or logic 0) using multiple transistors, such as 4T, 6T, 7T, 8T, 9T, or 10T configurations. Among these, the most commonly used SRAM type is 6T (six transistors).

SRAMs are often employed as cache memories, such as level 1 and level 2 cache memories, in processors. These cache memories operate synchronously with the processor at high speeds.

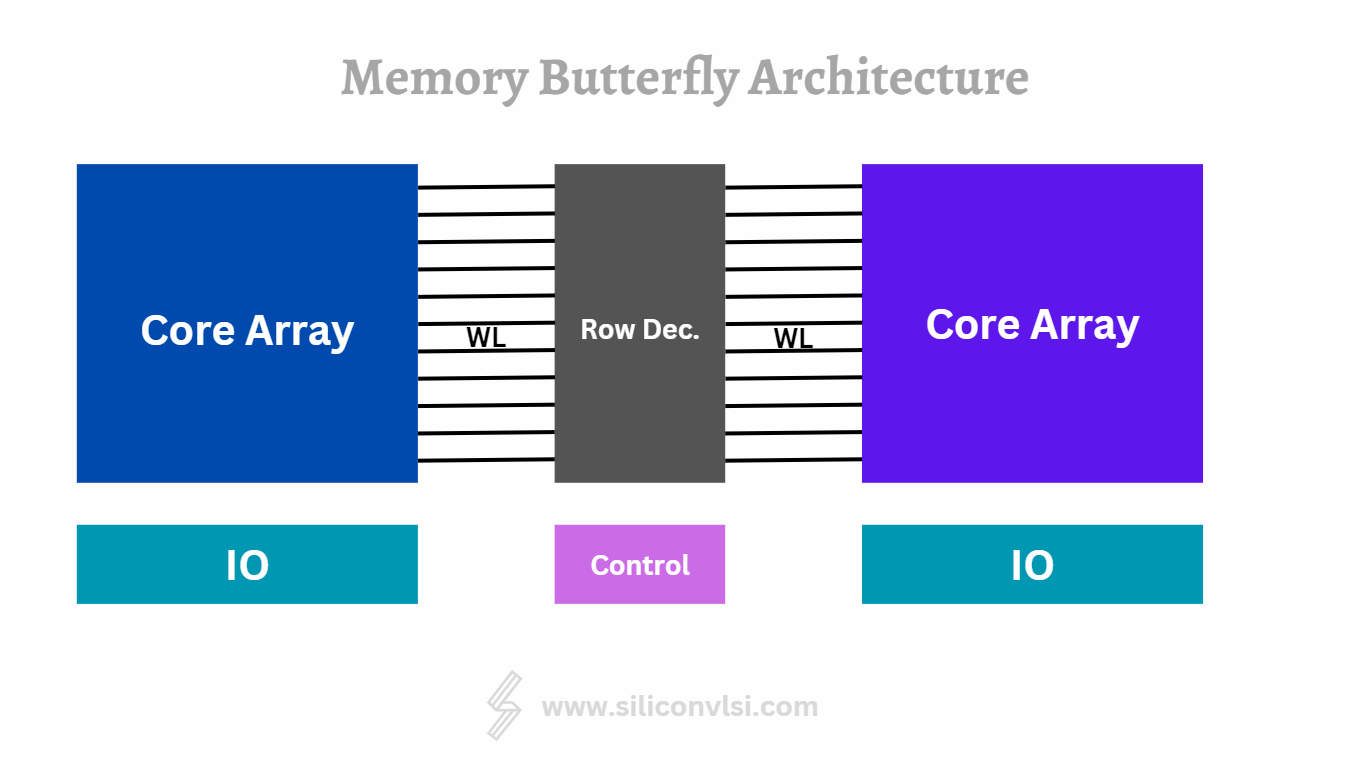

Figure 1 illustrates the typical architecture of SRAM, known as the butterfly architecture. In this architecture, the memory core array is distributed on the left-hand side (LHS) and right-hand side (RHS) of the row decoder. This arrangement reduces the load on the word lines by 50% compared to a single-ended architecture. Additionally, it decreases the RC delay of the WL (word line) signal reaching the corner bit-cells by 50%. The butterfly architecture is commonly utilized in SRAM designs to optimize performance and address the specific requirements of high-speed memory applications.

Advantages of SRAM Butterfly Architecture

Also Read:Memory Layout Interview Question

The Butterfly architecture in SRAM memory offers several advantages:

Reduced Word Line Load: By spreading out the memory across both sides of the Row Decoder, the Butterfly architecture reduces the load on the word lines by 50%. This reduction in load improves the overall performance and speed of the SRAM memory.

Decreased Delay: The Butterfly architecture also reduces the delay of the word line signal reaching the corner bit-cells by 50%. This decrease in delay enhances the speed and efficiency of the SRAM memory, allowing for faster data access and retrieval.

Improved Performance: The combination of reduced word line load and decreased delay leads to improved performance in terms of reading and writing data. The Butterfly architecture enables faster and more efficient data processing, making it ideal for high-speed memory applications.

Efficient Space Usage: The distribution of the memory across the Butterfly architecture optimizes space utilization within the SRAM memory. This maximizes the storage capacity of the memory while maintaining efficient access times.

Also Read: Memory Bank Architecture

Overall, the Butterfly architecture in SRAM memory provides benefits such as reduced word line load, decreased delay, improved performance, and efficient space usage. These advantages make it a valuable design choice for high-speed memory applications.