Layout Design Rules – (DRC)

DRC helps to check is an essential part of the physical design flow and ensures the design meets manufacturing requirements and will not result in a chip failure. Its stands for the Design Rule Check.

Various foundries have their own design rules for masking and They have consistent processes to convert GDS II into a real layout/final product.

According to technology and process information, they define some set of rules which has to follow by a Physical Design Engineer while delivering GDS II.

Process design rules are the minimum allowable drawing dimensions that affect the X and Y dimensions of a layout, but not the depth or vertical dimensions. Violating a design rule could lead to a non-functional circuit or lower yield.

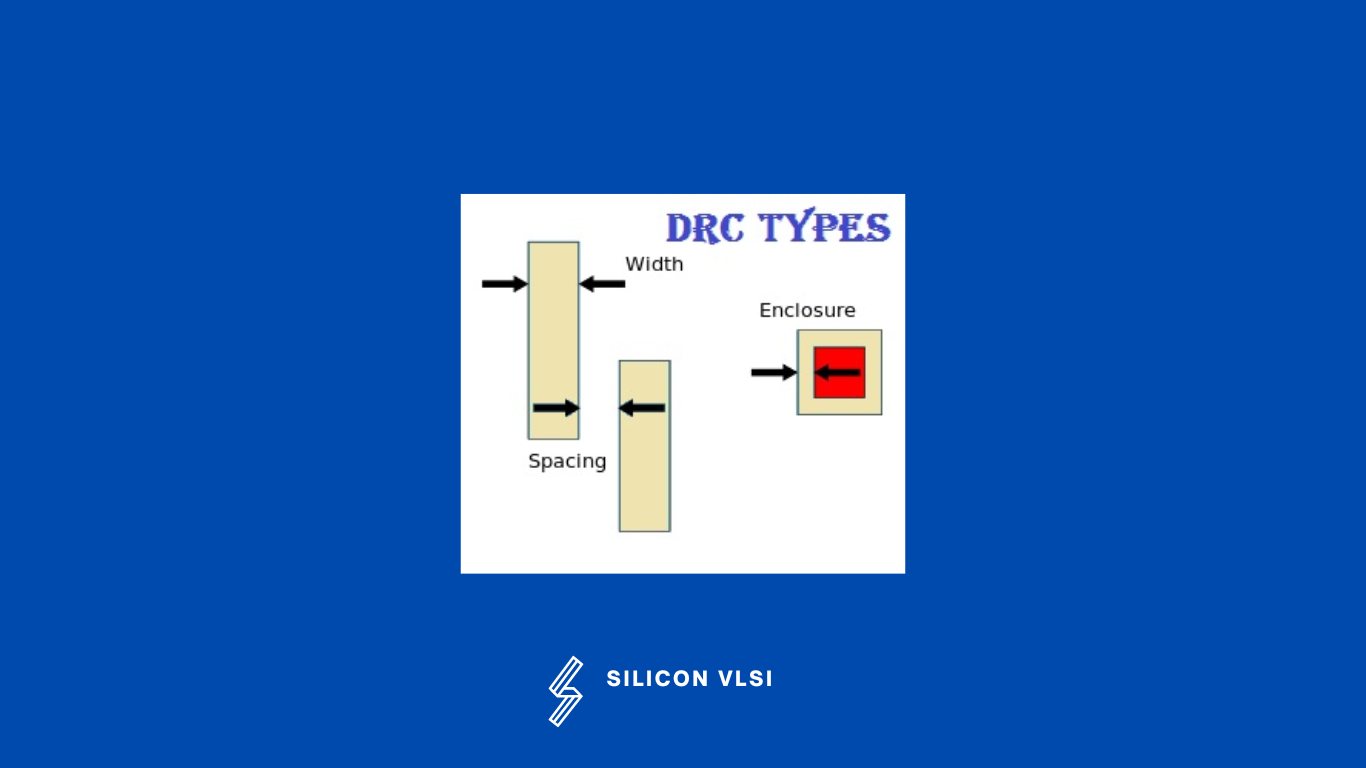

Types of Design Rule Checking

- Minimum width

- Minimum spacing

- Minimum area

- Poly Extension from diffusion

- Minimum width and spacing via

- Fat wire Via keep out Enclosure

- Different net spacing

- Shorts violation

- End of Line spacing

- Metal enclosure

- Wide metal jog

- Misaligned Via wire

- Center via spacing

- Special notch spacing

- Different net Via cut spacing