Depletion Region

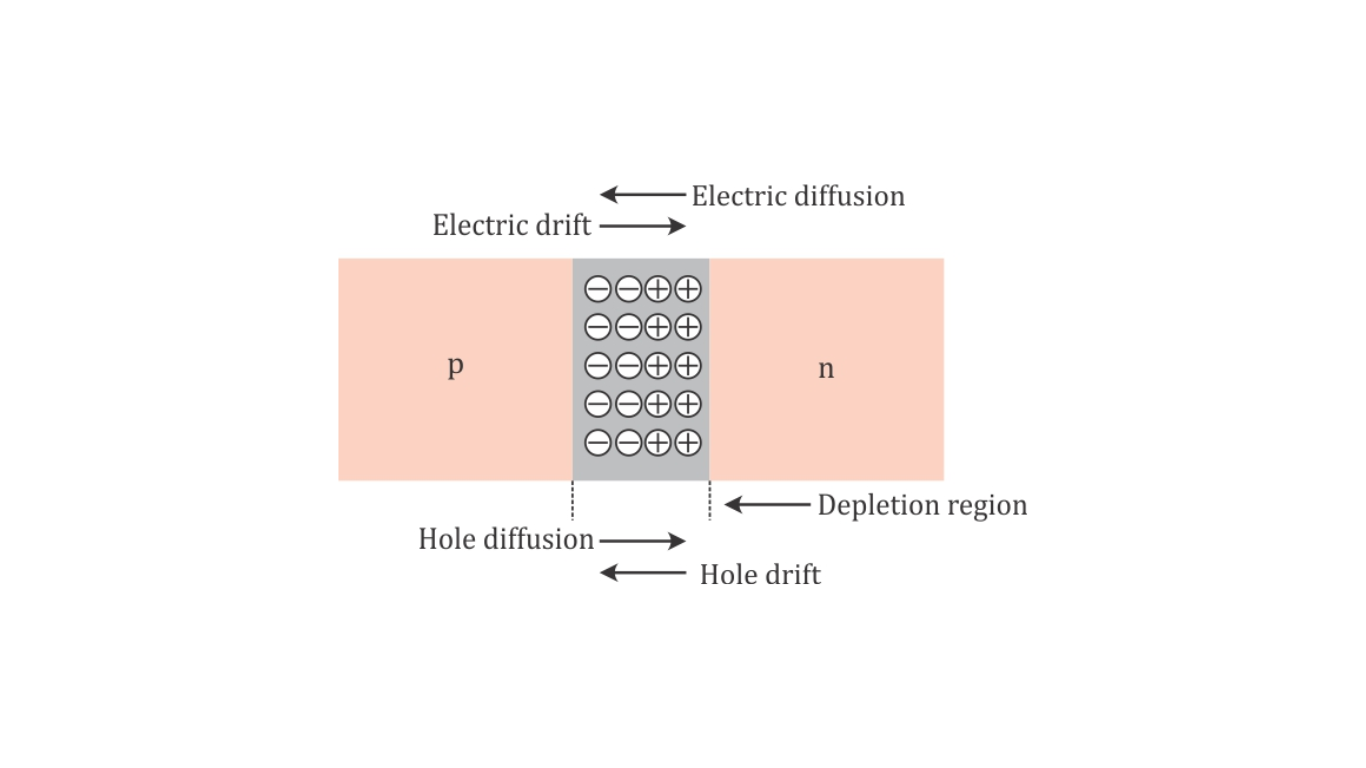

I find that the layer where the flow of charges slows down is called the Depletion Region. This region acts as a barrier to stop electrons from moving from the n-side to the p-side of the semiconductor diode.

We should understand that this barrier is crucial for the diode’s function, as it controls the flow of current through the device. You might notice that without this Depletion Region, the semiconductor diode wouldn’t work properly, as it wouldn’t effectively control the direction of current flow.

The junction between the p-type and n-type materials behaves differently from each side of the material alone when they are kept in contact with one another. At the junction, electrons and holes are in close proximity to one another. Coulomb’s law states that a force exists between the positive holes and the negative electrons. A few n-type electrons diffuse through the p-n junction during its formation, combining with the holes on the p-side to generate negative ions while leaving behind positive ions on the n-side. As a result, the depletion layer is created, acting as a barrier to prevent additional electron transport from the n area to the p region.