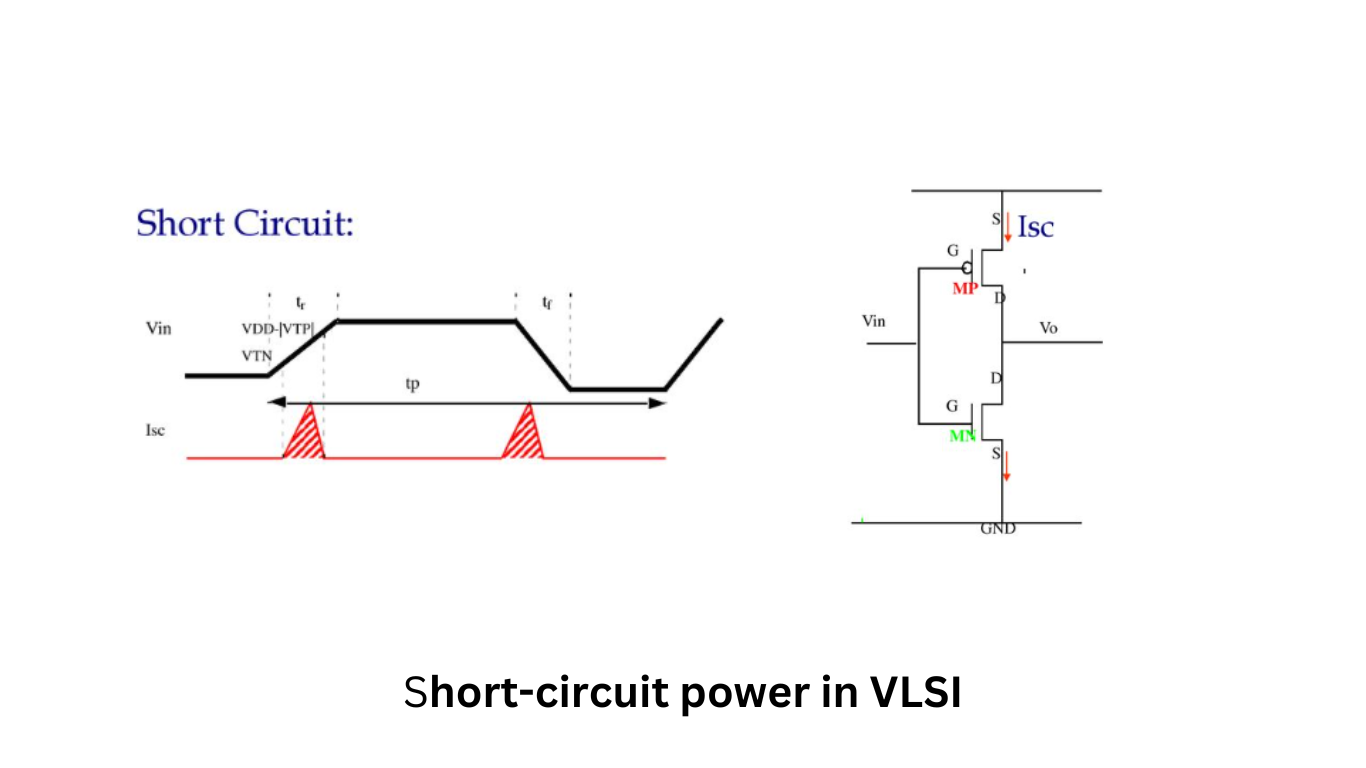

How You Can Reduce Short-Circuit Power in VLSI Design

Short-circuit power arises during the brief period when both the NMOS (N-channel metal-oxide-semiconductor) and PMOS (P-channel metal-oxide-semiconductor) transistors in a CMOS gate are simultaneously conducting while transitioning between logic states. Here are some techniques to mitigate short-circuit power: To bring this down, we can use a few smart techniques. For example, you can start by adjusting transistor sizes, optimizing threshold voltages, and reducing the input transition times.

I usually go with larger PMOS transistors with higher threshold voltages and smaller NMOS with lower thresholds. When we also make sure the input signals are well-controlled, we can significantly cut down on the short-circuit current and improve overall efficiency.

Gate Sizing

By adjusting the width of transistors in a CMOS gate, the short-circuit current can be controlled. Increasing the size of the PMOS transistor relative to the NMOS transistor can help balance the short-circuit current and reduce its impact.

Threshold Voltage Adjustment

Modifying the threshold voltage (Vt) of transistors affects their conductive behavior. A higher Vt for PMOS and a lower Vt for NMOS transistors can reduce short-circuit power.

Use of Low-Skew Clocks

Skew in clock signals can lead to overlapping transitions and increased short-circuit power. Employing low-skew clock distribution techniques can minimize such overlaps.

Logic Restructuring

By optimizing the logic structure of a circuit, the frequency of short-circuit paths can be reduced. This includes reducing redundant logic paths and avoiding logic configurations that cause excessive short-circuit current.

Advanced Circuit Design

Implementing techniques like dual-Vdd (multiple supply voltages) and power gating can effectively reduce short-circuit power.

Adoption of Clock Gating

Clock gating is a power-saving technique where the clock signal is disabled to certain circuit blocks when they are not in use. This prevents short-circuit power dissipation in those blocks during idle periods.

Pipeline Stages

Inserting pipeline stages in large circuits can break down long paths and reduce the probability of simultaneous short circuits.

By employing these approaches in VLSI design, the short-circuit power component can be effectively reduced, leading to more power-efficient and reliable electronic devices.