Latch-up in CMOS circuits

Latch-Up is a phenomenon where a low impedance path is created between a supply pin and ground due to unwanted noise. It is also called when minority carriers are injected into the substrate of a well.

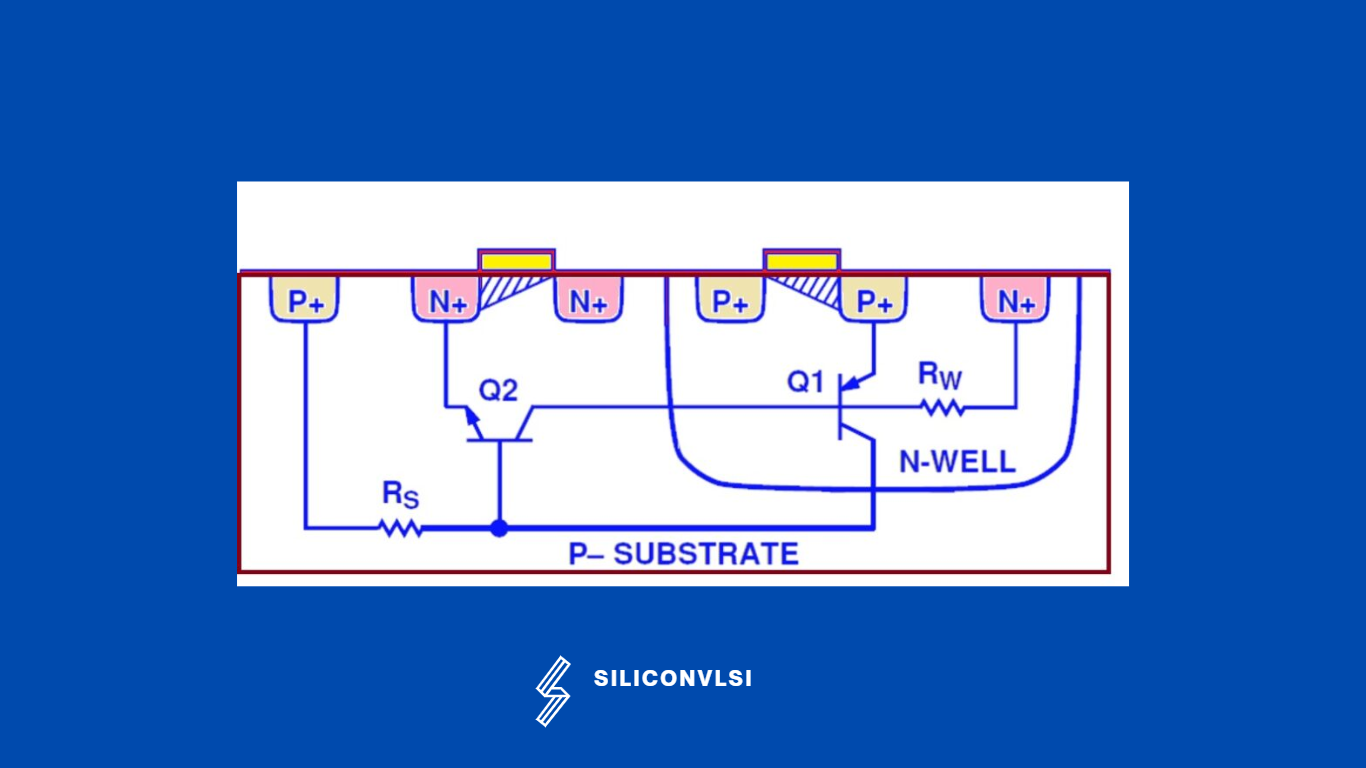

Latch-up Mechanism

The parasitic BJTs in the CMOS inverter structure form a positive feedback loop and are well known that the large collector current of a BJT is driven by a much smaller base current. Now, if for some reason a collector current flows in one of the BJTs, it will be fed into the base of the other BJT. This generates an even greater collector current in the latter BJT which is then fed into the former BJT. When the BJTs become locked in this runaway positive feedback process, they are said to be latched. In this latch-up condition, a low-impedance path is created between the VDD & VSS

Latch-up Causes

- Noise

- ionizing radiation

- If we put NMOS & PMOS closer

- Sudden changes in supply voltage

- Due to Minority charge carrier injection

- An electrostatic discharge (ESD) event can trigger the parasitic SCR

Latch-up Prevention Techniques

- Keep supply voltage below the maximum voltage.

- Keep NMOS & PMOS as far as possible.

- Use oxide trenches and buried oxide layers to isolate NMOS and PMOS devices.

- keep a Guard ring for the analog device and tap/bulk for the digital logic device.

- Use halo dopping

Why is a PMOS connected to a VDD and NMOS connected to the ground?

Because, to prevent latch-up in CMOS, the body-source and body-drain diodes should not be forward-biased. For example, the body terminal should be at the same or lesser voltage than the source terminal (for an NMOS) & for PMOS.