NMOS Inverter

The MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) is a versatile electronic component widely used as a switch in various electronic applications. It offers advantages over mechanical switches in terms of speed and reliability. In this context, the MOSFET switch is also known as an inverter.

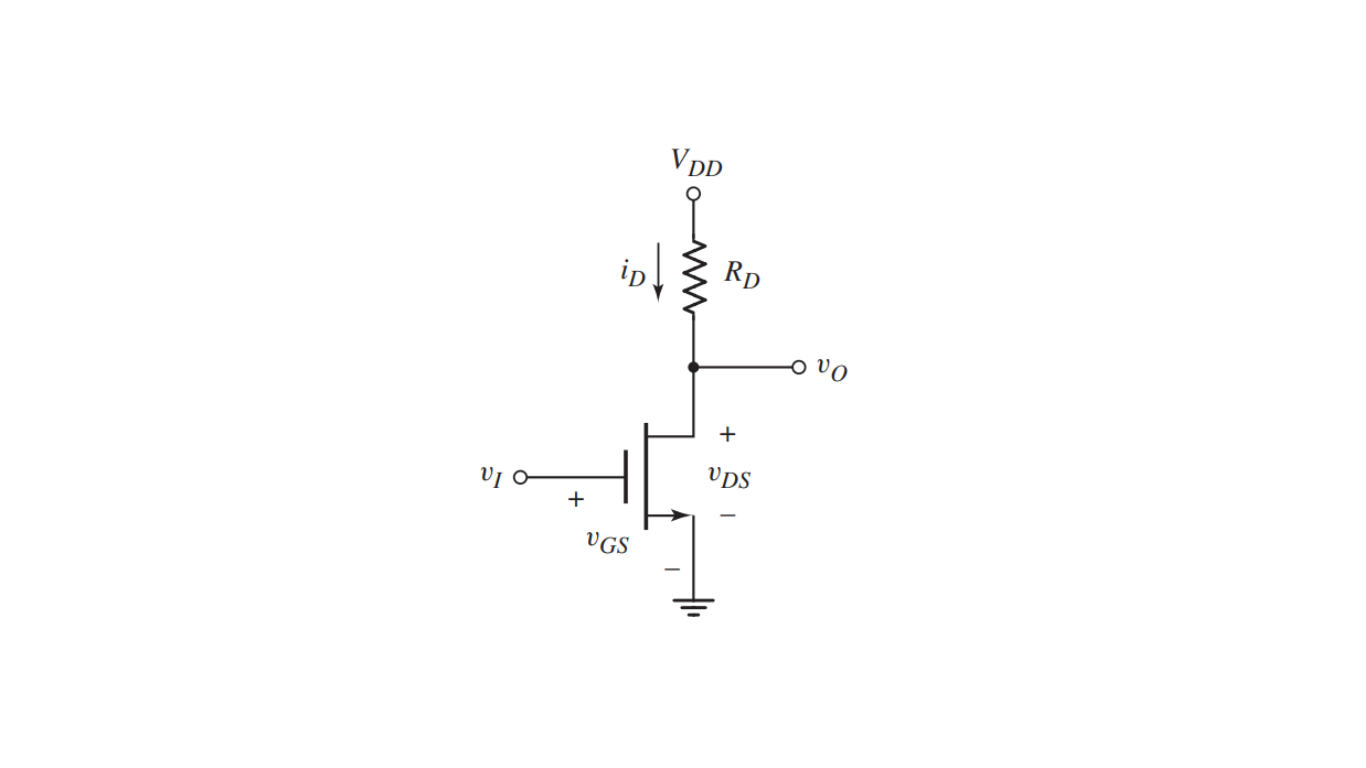

Understanding the NMOS Inverter Circuit

The figure illustrates the circuit of an n-channel enhancement-mode MOSFET inverter. When the input voltage, vI, is less than the threshold voltage, VT_N, the transistor is in cutoff mode, and the drain current, iD, is zero. Consequently, there is no voltage drop across RD (drain resistor), and the output voltage, vO, becomes equal to VDD (supply voltage). Since there is no drain current (iD = 0), no power is dissipated in the transistor.

When the Transistor Turns On

On the other hand, when the input voltage, vI, is greater than the threshold voltage, VT_N, the transistor is turned on, initially biased in the saturation region, as vDS (drain-to-source voltage) is greater than vGS – VT_N. As the input voltage continues to increase, the drain-to-source voltage decreases, and the transistor eventually moves into the non-saturation region.

Maximum and Minimum Values

At vI = VDD, the transistor is biased in the non-saturation region, vO reaches its minimum value, and the drain current, iD, reaches its maximum value. The expressions for the current and voltage are as follows:

iD = Kn * (2(vI – VT_N) * vO – vO^2)

vO = VDD – (iD * RD)

where vO represents vDS and vI represents vGS.