Triple-Well Processes

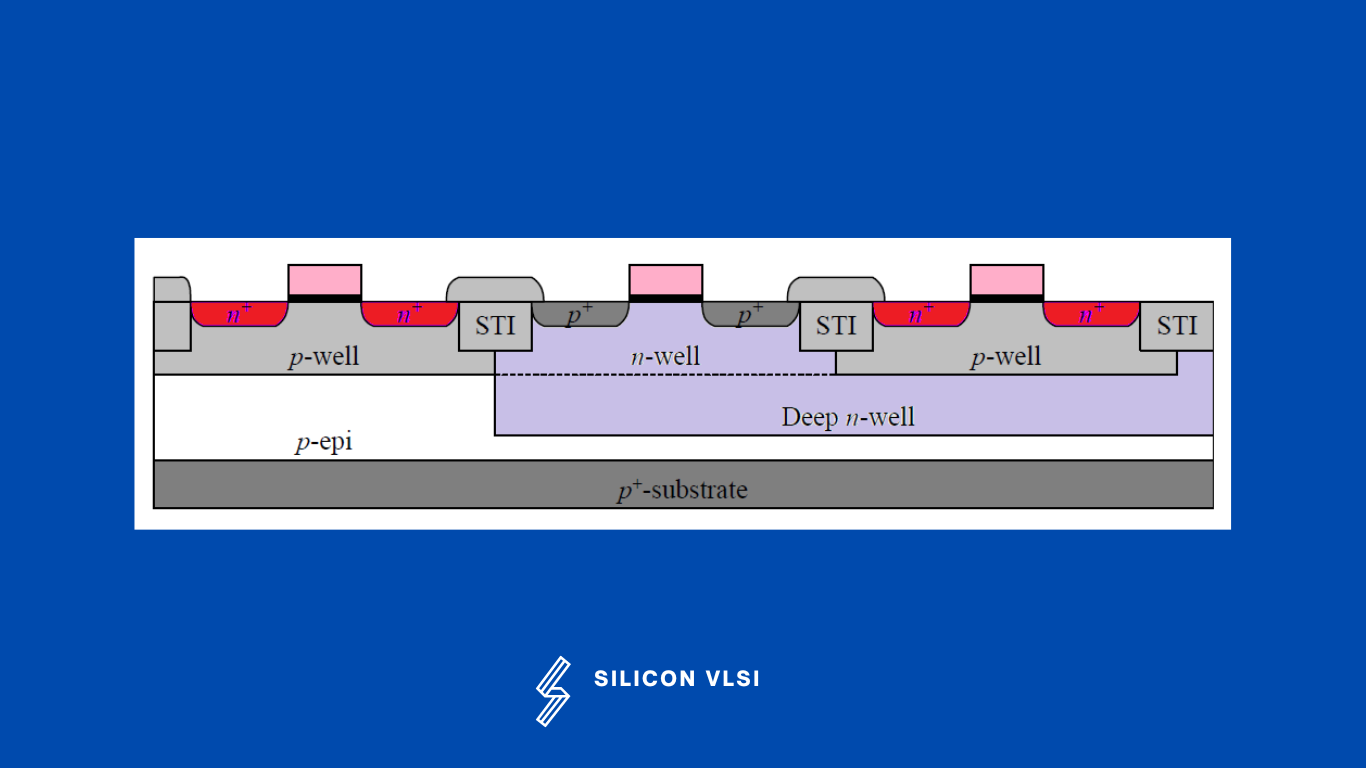

Triple-Well Processes are used to isolate the most sensitive circuit in Analog Layout Design. A triple-well structure contains at least one p-well in a p-type substrate, and a number of deep n-wells, and inside the deep n-well, a p-well is formed as shown in Following Figure 1.

Why we need Triple-well structure in CMOS.

As we know that we are using Guarding and Epitaxial Layer in Analog Devices for device isolation purposes, but it helps to provide isolation from the surface only, Because of coupling capacitance, and capacitance from the substrate or ground side, we need Tripe Well structure in CMOS.

Triple-Well Fabrication Processes.

The triple-well structure can be formed using either diffusion, called the diffused triple well, or high-energy ion implantation called the retrograde triple well. Due to many advantages over the diffused triple well, the retrograde triple-well structure has dominated and been widely used in modern CMOS devices, including memory and embedded memory.

The first Fabrication step is, too deep the n-well is fabricated by ion implantation, with high energy, Second step is to fabricate N-well and P-well(inside the deep n-well). The process for fabricating the triple-well structure begins to form deep n-wells with high-energy ion implantation in the p-type substrate at a depth.

The n-well mask is subsequently used to form n-wells at a depth of about 1 mm where p-type MOS transistors are to be fabricated. The threshold voltage adjustment of pMOS transistors is also done in this step. Then, the p-well mask is employed to form p-wells where n-type MOS transistors are to be fabricated. These p-wells are at about the same depth as n-wells. The threshold voltage adjustment of nMOS transistors is also done in this step. Finally, a high-temperature drive-in process is applied to form p-wells and n-wells.

Advantages of triple-well process

It helps to avoid coupling capacitance from the substrate or ground. #

It also avoids band-to-band leakage current at the source junction during the erase operation.

It provides an electrically isolated P-well in order to reduce the electronic noise and cross-talk from the substrate.

Epitaxial Layer

An epitaxial layer wafer provides a low-resistance substrate that helps significantly to reduce the possibility of latch-up.

![]()