Leakage Current in CMOS

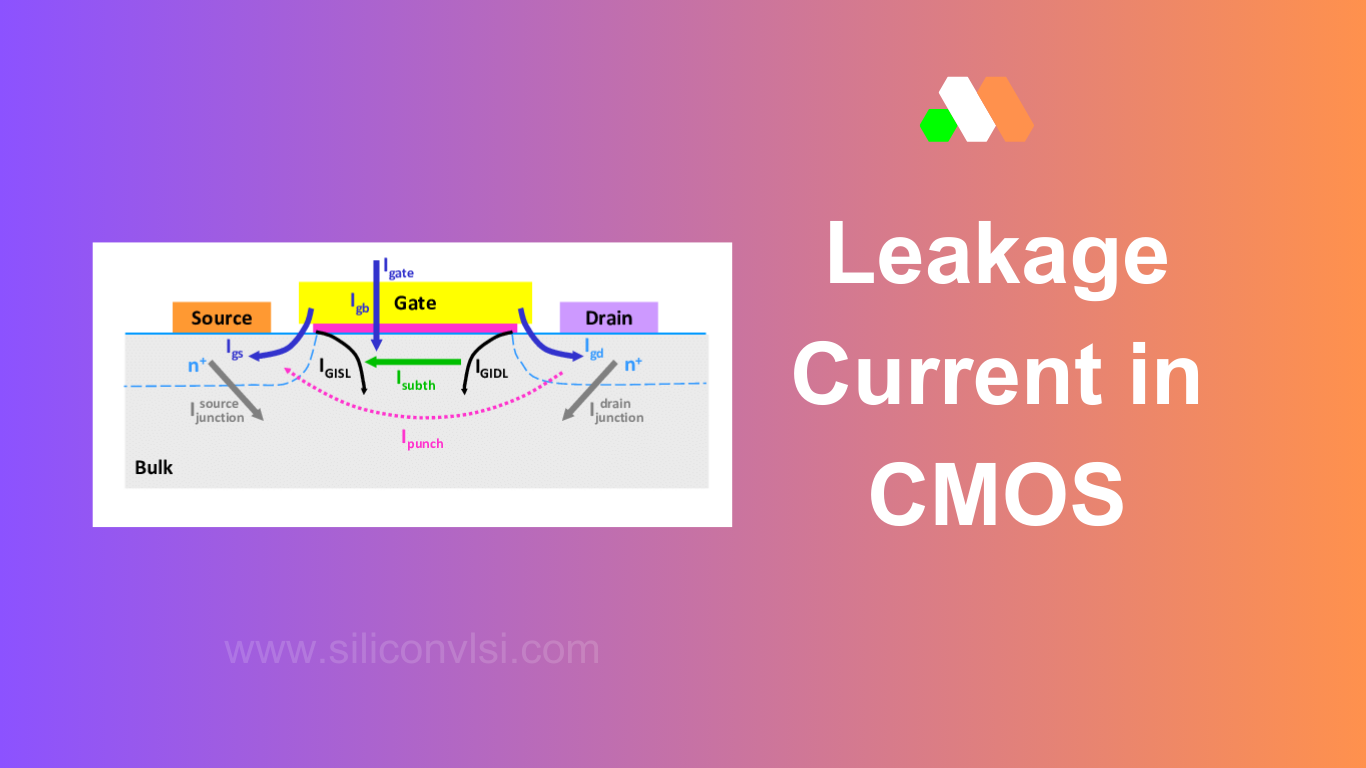

Leakage current in a CMOS (Complementary Metal-Oxide-Semiconductor) transistor refers to the unwanted flow of electric current between the drain and source terminals of the transistor when it is supposed to be turned off or in a non-conductive state. Leakage currents can have a significant impact on the power consumption and overall performance of electronic circuits. There are four main types of leakage currents in a CMOS transistor:

Subthreshold (Weak Inversion) Leakage

- Subthreshold leakage current occurs when a transistor operates in the weak inversion region.

- It is caused by the diffusion of minority carriers (electrons for NMOS and holes for PMOS) in the channel of the MOS structure.

- When the gate voltage (Vgs) is below the threshold voltage (Vth), the transistor is in the off state, but a small amount of current still flows due to subthreshold leakage.

Reverse-Biased Source/Drain Junction Leakage

- In an NMOS transistor, there exists a reverse-biased p-n junction formed by either the source or drain connected to the substrate when the transistor is off.

- Despite the potential barrier, there is a leakage current.

- This leakage current consists of two components: electron-hole generation in the depletion region and minority carrier diffusion/drift at the edge of the same depletion region.

Gate Direct-Tunneling Leakage

- Gate direct-tunneling leakage current is a result of current tunneling into the gate of the transistor.

- The tunneling mechanisms include electron conduction band tunneling (ECB), electron valence band tunneling (EVB), and hole valence band tunneling (HVB).

- ECB is the dominant phenomenon and occurs due to high electric fields across the oxide layer, leading to electron tunneling through the gate oxide.

Gate-Induced Drain Leakage

- Gate-induced drain leakage (GIDL) current is directly related to the high electric field effects in the drain region of a MOS transistor.

- For instance, in an NMOS transistor with its gate grounded and drain at a supply voltage potential, energy band bending occurs in the drain.

- This bending allows electron-hole pairs to be generated through avalanche effects and carrier tunneling between energy bands.

- Holes are quickly driven to the body region, creating a deep depletion situation, while electrons are collected in the drain.

- These effects collectively result in the IGIDL current.

These different leakage currents represent the various mechanisms by which unintended current flows through a transistor even when it is not actively conducting according to its intended logic state. Managing and minimizing these leakage currents are critical challenges in modern semiconductor design to reduce power consumption and improve the efficiency of electronic devices.