Standard Cell Library for ASIC Design

- Standard cells are designed based on power, area, and performance(PPA), which is used in digital cell libraries. Standard cells are the pre-defined, pre-characterized, and pre-verified cells, Standard cell architecture is defined based on cell height which is determined on the basis of a number of tracks, beta-ratio, pitch, and transistor widths.

How do you decide the height of Standard cells?

The track is generally used as a unit to define the height of the std cell. The track can be related to lanes.

Standard cell height = Pitch * (N-1) where N represents the number of tracks.

What is Pitch?

The distance between two tracks is called a pitch.

Component of generic library

- Basic gates (AND, OR, NAND, NOR, INV, EXOR, EXNOR)

- MUX

- AOI

- OAI

- Fillers, Tap cells, End Cap, Decap cells

- Tie CellsBoolean function cells

- Flip-Flops

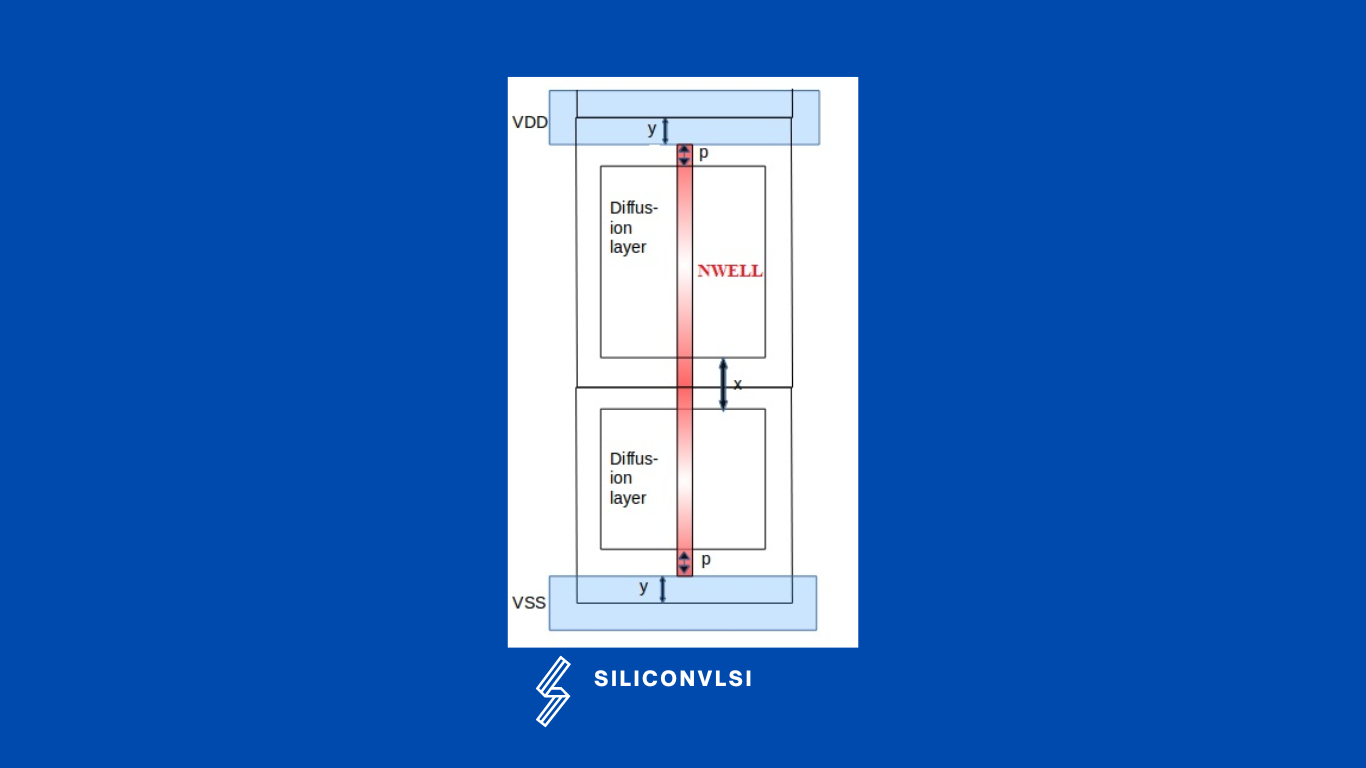

Tap cells

- Tap cells are used to provide substrate connection.

- They are used to avoid latch-up violations.

- They connect n-well to VDD and p-sub to VSS.

- It is also used to fill the gap between two std cells.

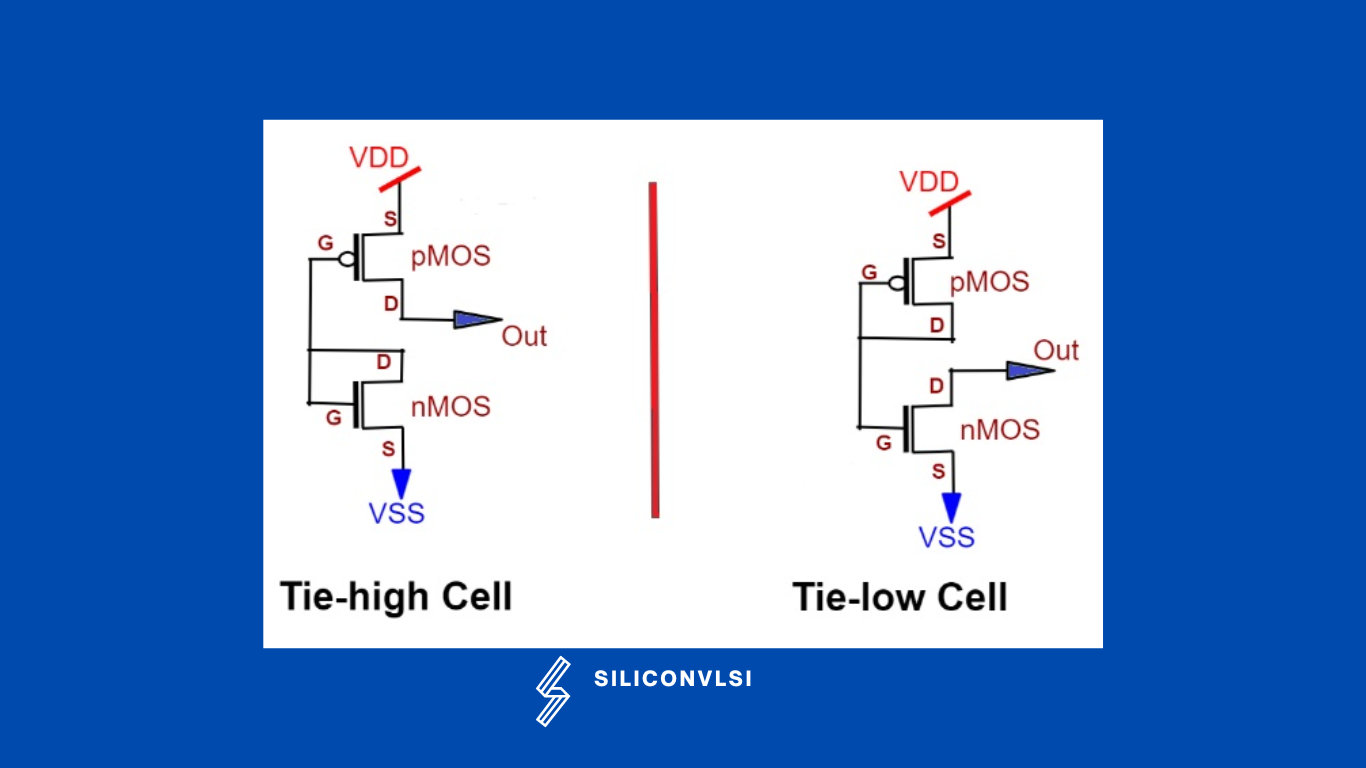

Tie cell

- Tie cells are used to avoid direct gate connection to the power or ground network thereby protecting the cell from damage.

- In Design, some cell inputs may require a logic 0 or logic 1 value. Instead of connecting these to the VDD/VSS rails/rings, you connect them to special cells available in your library called tie cells library.

- There are the following two types of Tie cells

- Tie High cell: Tie high cell, nmos acts as diode-connected and gives logic 0 to the gate of pmos, so we will get logic 1 as output

- Tie Low cell: Tie low cell, pmos act as diode-connected and give logic 1 to the gate of nmos, so we will get logic 0 as output.

Filler cells

- Filler cells are used to provide power/ground rail continuity, and n-well continuity so that DRC violations will not come

- They contain n-well and p substrate.

- Filler cells primarily are non-functional cells used

Decap cells

- Decap cells also called Decoupling capacitor cells

- When there is a drop in power rail, these cells act as a battery and maintain the voltage across rails.

- These cells aid the IR drop issue and remove glitches in power.

- Decap cells are capacitors added in the design between power and ground rails.

End cap cells

- End cap cells are added near the end of rows to terminate the rows properly.

- The n-wells of end cap cells are properly terminated within the cell.

- End cap cells are used for DRC purpose

What is a standard cell used for?

A standard cell is a collection of transistor and interconnect structures that performs a specific boolean logic function (such as AND, OR, XOR, XNOR, or inverters) or a storage function (flip-flop or latch).