What is a filler cell?

Filler cells primarily are non-functional cells used to continue the VDD and VSS rails. Filler cells are used to establish the continuity of the N- well and the implant layers on the standard cell rows. The use of Filler Cells is they reduce the DRC Violations created by the base(N-Well, PPlus & NPlus) layers. and also help maintain the Power Rail, VDD/VSS connection continuity.

What is the need for filler cells?

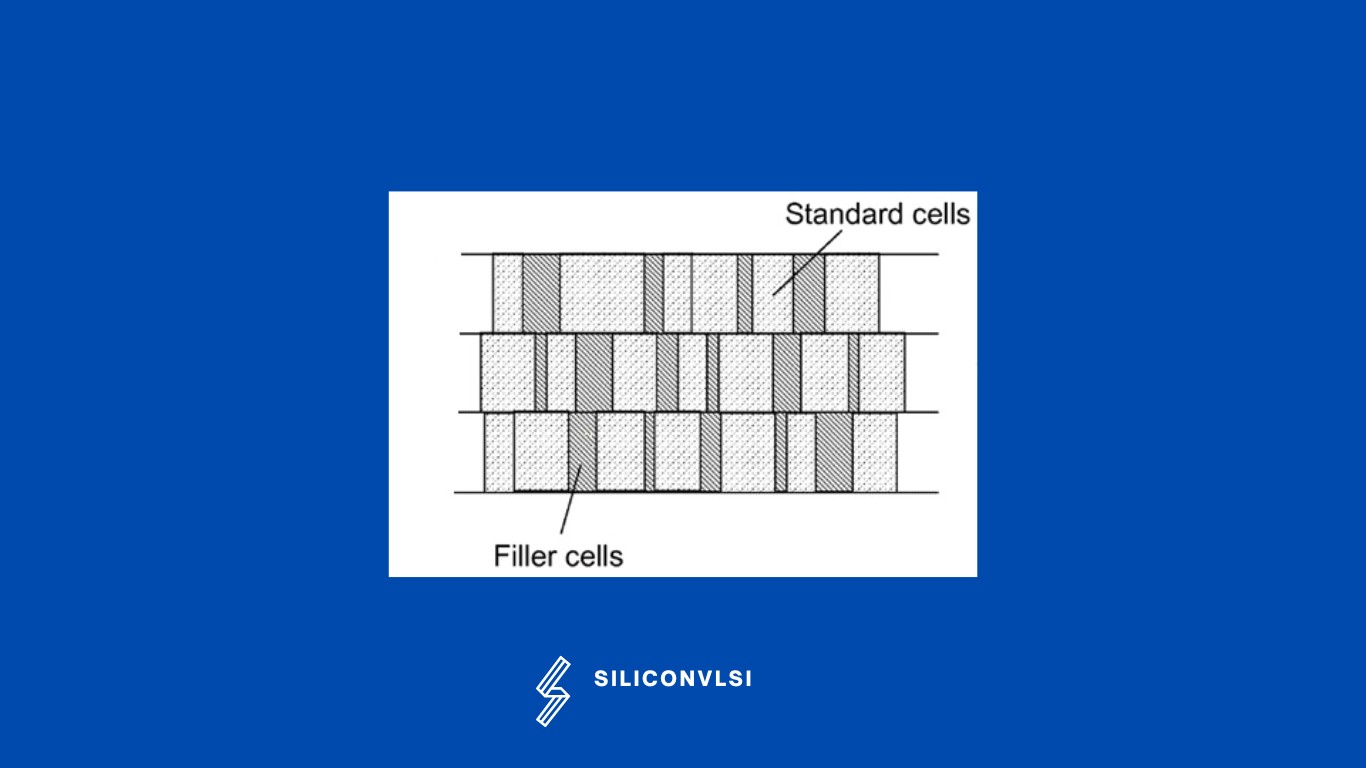

Filler cells are used for connecting the gaps between the cells after placement. In APR flow, the cells in the design are placed on a row. To make sure that each cell gets power and ground connection, the cells are abutted together so that the VDD and VSS rails are continued short together. This makes it possible to tap power only at one point anywhere in the row. But it is virtually impossible to fill 100% of the die area, we use filler cells to fill these spaces between regular library cells to route power rails.

What is continuity and Why is it needed?

There are 3 types of continuity :

- N-well,

- P-well &

- Power continuity.

Continuity is needed for DRC clean purposes in Standard cells abutment. Also, the wells need to be tied to a single global VDD/VSS so as to tap power only at one point anywhere in the standard cell row.

What will happen if we don’t insert filler cells?

Basically, filler cells will make Power/Ground and N-well continuity. There will be power/ground open between the standard cells(empty space) and also may be N-well spacing or abutment DRC error may come if we do not use filler cells in between standard cells.

What are the other uses of Filler cells?

They have power rails, N-well, PPlus, and NPlus layers only. It will be used for Engineering Change Order (ECO)’s, then the filler cells can be deleted and the empty spaces can be utilized. They can also be used to cope with setup or hold violations. It will also help to prevent density-related DRC errors for base layers(FEOL). but Filler cells don’t play any role in Latch-up prevention. For Latch-up prevention, we use TAP cells

Why do we use endcap cells?

In VLSI design, end cap cells are strategically placed to protect regular cells’ gates located near the border from manufacturing damage. They help prevent violations of the boundary’s base layer DRC (Design Rule Check), including Nwell and Implant layer constraints. Additionally, end cap cells ensure proper alignment of adjacent blocks with the boundary cells.