Fixing Double-patterning Errors in FinFET(2024)

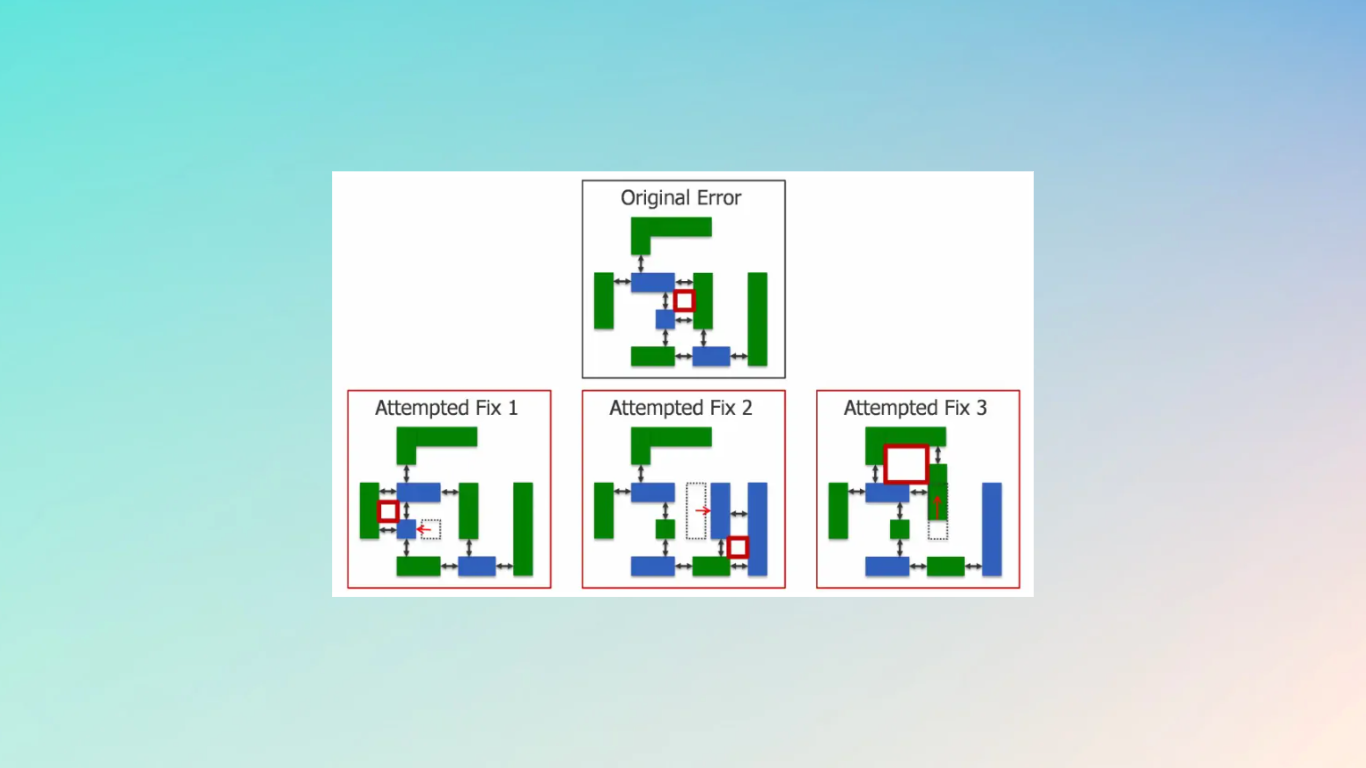

The so-called odd-cycle path is the most typical double patterning error. This occurs when an odd number of polygons are placed in a loop with a minimum spacing between them (technically, a spacing close enough to call for the polygons to be on separate colored masks).

G0(GNOT) Error in VLSI

In the most basic scenario, three polygons must each have a different color from the other two, which is obviously difficult given that there are only two colors available. It is important to stress that there are multiple violations, not simply one involving spacing or one involving color. The polygons are impossible to color correctly. The violation is indicated by a square (or more complex polygon for more complex violations) that identifies the cycle’s polygons rather than using a fictitious coloring to call attention to one of the violations as “the” error (as in the above picture).

How to Fix Double-patterning Errors

The violation can be fixed by either increasing spacing so as to break the cycle, or by removing a polygon completely, either breaking the cycle or making the cycle even (which is not a problem since it can be colored).

Of course, a real layout could contain both anchor path violations and odd path violations in the same area of the design. David suggests focusing on the unusual cycle path violations first because they frequently correct some of the anchor path violations anyhow. Consider your anchor path violations after that.

Why do we go for FinFET?

FinFETs have a structure that results in lower leakage power and higher device densities. They provide a high drive current and work at a lower voltage as well. By combining these factors, substantially more performance may be fit into a smaller space, lowering the cost per unit of performance.