What is Gate-All-Around (GAA)?

In, Gate-all-around, the gate contacts the channel from all sides and enables continued scaling. Such transistors are referred to as gate-all-around, or GAA, transistors.

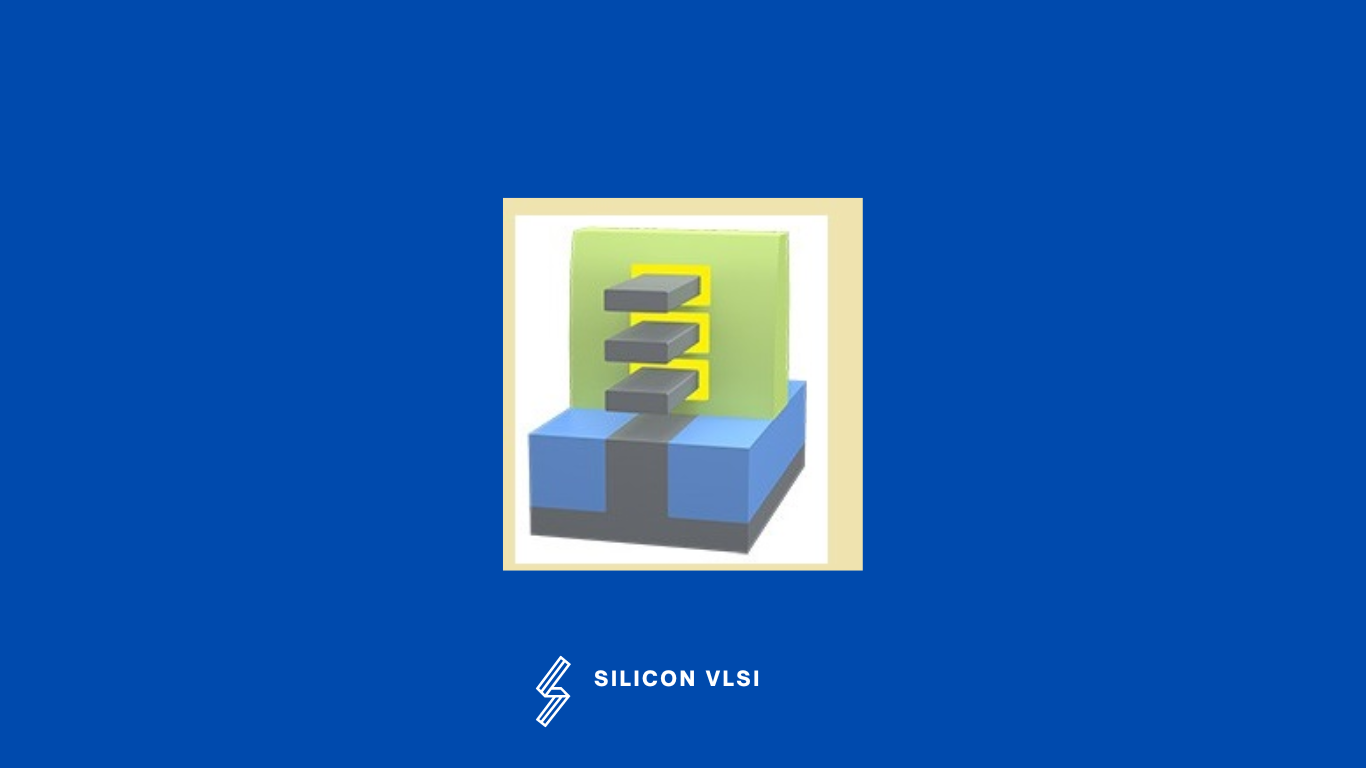

Vertically stacked nanosheets will be used in the first GAA devices. They are made of distinct horizontal sheets and have gate materials all around them. Comparatively speaking, this offers better channel control than finFETs. The current-carrying capacity of GAA transistors is improved by stacking a few nanosheets vertically with gate material encircling the channels, in contrast to finFETs where more current requires numerous side-by-side fins. Transistors can be sized for the precise performance needed by scaling the nanosheet dimensions.

What Is GAAFET?

The first GAAFET, which was a vertical nanowire GAAFET and was known as a Surrounding Gate Transistor, was unveiled by Toshiba in 1988. The function of a Gate-All-Around Field Effect Transistor (GAAFET) is identical to that of a FinFET transistor, except that the gate material completely encircles the channel.

In general, GAAFETs can have two or four gates depending on the architecture. As it offers greater device performance at smaller sizes, such as below 7 nm, Gate-All-Around Field Effect Transistor (GAAFET) technology is thought to be the FinFETs‘ replacement. GAA transistors are created using nanowire and nanosheet architectures. Depending on the implementation, the orientation of the GAAFET structures might be parallel or perpendicular to the substrate.

In GAA, The gate contacts the channel created using nanowires and nanosheets on all four sides, offering better control over the channel characteristics than a conventional FinFET. The GAAFET semiconductor device uses layers of silicon that are spaced apart from one another rather than a fin that extends from the substrate.

Advantages of Gate-All-Around (GAA)

Use of Gate-All-Around (GAA) is despite having superior performance over earlier FET types, GAAFET semiconductor devices require more sophisticated production processes. Starting with the growth of a superlattice comprising alternating Si and SiGe epitaxial layers, a nanowire GAAFET is created.

The nanosheets and nanowires are built upon these layers. To protect the drain and source areas and retain superior control over the gate width, an inner dielectric spacer layer is placed. Gate metal and gate dielectric are used to fill the open gaps between the nanosheets.

FinFET to GAA Transition

Companies were forced to transition to FinFETs due to the constantly evolving nature of manufacturing technology, but it appears that these transistors have reached a size threshold at which further shrinking is difficult and the performance gain is minimal. The transistor’s operating conditions are being hampered by the short-channel effects, which have lowered the control over leakage current.

Why GAAFET?

- GAAFET transistors offer devices that are extremely effective. Leakage current is minimal and short-channel effects are minimal because of the increased channel size and architecture.

- The nanosheets’ width and quantity can be adjusted. As a result, engineers have a greater understanding of the device’s characteristics. For example, a wide sheet will generate more current but increase the cost as a whole. The driving current can be decreased if the makers choose to minimize the gadget size. Additionally, GAA technology has assisted in further reducing voltage scaling, which was previously constrained in FinFET due to design limitations.

- Device sizes have shrunk as a result of the development of more advanced manufacturing techniques and the demand for effective gadgets. However, when transistors got bigger, short channel effects, leakage from quantum tunneling, and mobility degradation got worse.

- FinFETs, which introduced a 3-D architecture as opposed to a planar device, gave a mechanism to more effectively regulate the dynamics of the device. Due to the design characteristics, FinFETs were highly scalable, reduced leakage currents, and offered quicker switching times.

Gate-All-Around (GAA) fabrication steps

There are basically three main fabrication steps:

Step 1:

In order to create the nanosheets that serve as the foundation for the GAA transistors, a superlattice of alternate Si and SiGe epitaxial layers must first be grown.

![]()

Step2:

Critical steps include the deposition of an inner dielectric spacer to protect the source/drain regions and define the gate width, as well as the channel release, and etch to remove the sacrificial layers. The gate dielectric and metal, including between the nanosheets, must then be inserted into the space created by the removal of the sacrificial layers.

![]()

Step3:

For the gate metal, new materials are probably going to be introduced. Some producers are considering cobalt along with ruthenium, molybdenum, nickel, and other alloys.

![]()

GAA transistors Future

The replacement for FinFETs will be GAA transistors, with nanosheets turning into nanowires. The advanced process nodes currently listed on the roadmap should continue to use these GAA structures.

Transistor architectures have advanced significantly since the first planar architectures. The progress and the amazingly smart and connected world they have made possible would have surprised those early pioneers. The gate-all-around transistor will likely bring new end-user devices and capabilities, which we anticipate.