Fabrication Step In VLSI

VLSI full form is (very-large-scale integrated circuit) technology, In the late 1970s, non-self-aligned metal gate MOSFETs with gate lengths in the order of 10μm were the norm. The current VLSI fabrication technology is already at the physical scaling limit with gate lengths in the 20-nm regime. One of the reasons why we are using silicon in VLSI Technology is, Sand naturally contains silicon, an element that is abundant.

It can be improved. employing standard crystal growth and purification methods. It also displays the appropriate physical characteristics needed to create active devices with good electrical properties. In addition, silicon is quickly oxidized to produce SiO2, a superior insulator. This Native oxide is useful for making MOSFETs and capacitors.

IC Fabrication Steps

The next sections will outline the fundamental IC fabrication steps. A few of these actions may be performed repeatedly, in various combinations, and under various processing circumstances

a full fabrication cycle.

Silicon Wafers

Modern integrated circuits are made of single-crystal silicon, which is a very high-purity material. The substance is originally generated as a single ingot of crystal. It has a steel-gray solid cylinder shape that can range in diameter from 10 cm to 30 cm and in length from one to two meters.

A micrometer, or micron, is a millionth of a meter, and this crystal is sawed (like a loaf of bread) to create round wafers that are 400 to 600 micrometers thick. Then, using chemical and mechanical polishing (CMP) methods, the wafer’s surface is polished to a mirror sheen. Semiconductor makers often buy silicon wafers that are already produced by a supplier and hardly ever begin their fabrication process with ingots.

Oxidation

Oxygen and silicon interact during oxidation to create silicon dioxide. It is important to conduct the oxidation at high temperatures (for example, 1000–1200°C) and within ultraclean furnaces in order to hasten this chemical reaction. It is vital to work in a clean room to prevent the entrance of impurities of any size, which could drastically change the electrical characteristics of silicon.

To make sure that there is no dust in the airflow in the processing area, particle filters are utilized. Wearing specific lint-free attire that covers them from head to toe is a must for all staff members in order to safeguard the clean-room environment.

Wet oxidation tends to grow more quickly, whereas dry oxidation produces better electrical properties. in a thermal Excellent electrical insulating characteristics are present in the developed oxide layer. SiO2 has a dielectric constant of roughly 107 V/cm. It can be utilized to create top-notch MOS capacitors and has a dielectric constant of around 3.9.

Additionally, silicon dioxide has the ability to effectively mask a variety of contaminants, limiting the entrance of dopants into silicon to areas that are not covered with oxide. The surface of silicon is extremely reflective, and silicon dioxide is a transparent coating. The wavelengths of the reflected light depend on the thickness of the oxide layer when white light is flashed on an oxidized wafer to produce constructive and destructive interference.

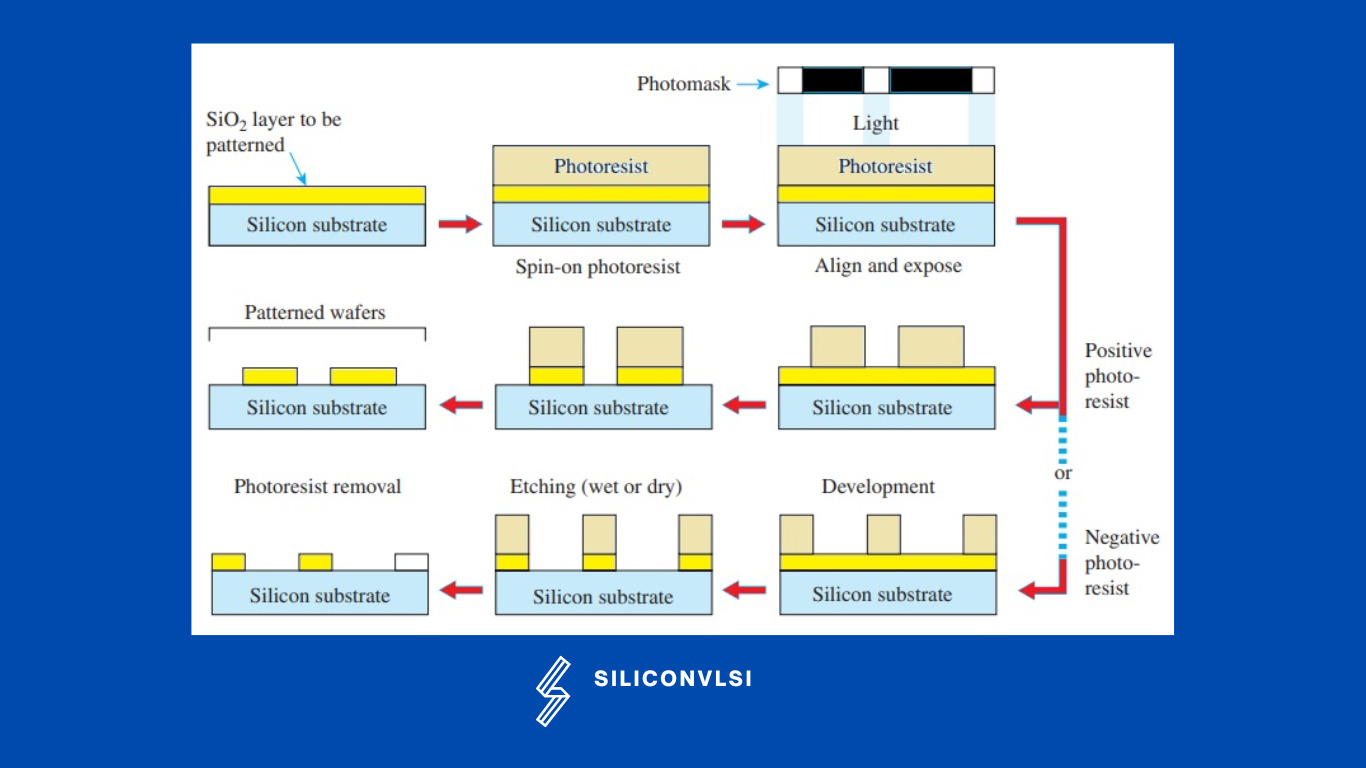

Photolithography

Using the spin-on method, a photosensitive layer known as a photoresist is applied to the wafer surface. The photoresist will then be selectively exposed using a photographic plate with painted patterns using deep ultraviolet irradiation. The patterned photoresist layer works well as a masking layer to shield the materials underneath from reactive ions or wet chemical etching.

Utilizing the proper etching techniques, silicon dioxide, silicon nitride, polysilicon, and metal layers can be selectively removed. The photoresist is removed following the etching step(s), leaving the photomask’s permanent pattern on the wafer surface. The Difference Between Positive and Negative photoresists are following

Positive and Negative Photoresists

Positive Photoresists

In Positive Photoresist, The chemical structure of the photoresist changes when it is exposed to UV light, making it more soluble in the photoresist developer. The underlying material is then exposed once these exposed portions have been removed using the photoresist developer solvent.

The photoresist developer is unable to dissolve the portions of the photoresist that are not exposed to UV light. The design is duplicated and exposed as a mask on the wafer when you deal with positive photoresists in the semiconductor manufacturing

Negative Photoresists

It is a perfect opposition to positive photoresists. Negative photoresists become very difficult to dissolve rather than more soluble. As a result, the photoresist developer solution works to remove the unexposed portions while leaving the UV-exposed negative resist on the surface. This results in a mask that is applied to the wafer and has the original design reversed.

Both positive and negative photoresists are still utilized in the semiconductor production sector today, but because positive photoresists have superior resolution capabilities, many semiconductor vendors choose them.

Because the photoresist developer solution doesn’t penetrate the regions that haven’t been exposed to UV light, positive photoresists can preserve their shape and pattern. Negative resists can cause pattern distortions because the solvent permeates both the UV-exposed and -unexposed portions.

Etching

The photographic patterns can be permanently etched onto the wafer using chemical (wet) etching or RIE dry etching techniques. Wet etching is the common name for chemical etching. The removal of several layers can be accomplished using various chemical solutions. For instance, SiO2 can be etched using hydrofluoric acid (HF), silicon can be etched with potassium hydroxide (KOH), aluminum can be etched with phosphoric acid, and so on.

The chemical typically assaults the exposed areas during wet etching that are not covered by the photoresist layer from all sides. We can say that RIE(Reactive-ion etching) is a type of dry etching that has different characteristics than wet etching. RIE uses chemically reactive plasma to remove material deposited on wafers. Anisotropic Etching vs. Isotropic Etching are following,

![]()

Isotropic Etching

The isotropic etching includes all etching processes with equal etch rates for all spatial directions. Isotropic etch processes are rate-controlled either by transport processes with direction-independent transport rates (the most common example of isotropic etching) or by surface processes. Both wet chemical procedures and dry etching processes are used in isotropic etching. The problem with isotropic etching is that it is suffering from the undercut, as shown in the above figure

Anisotropic etching

Anisotropic etching is a subtractive microfabrication technique that aims to preferentially remove material in one direction to obtain intricate and often flat shapes. The significance of dry plasma etching for usage in anisotropic processes can be attributed to the fact that it is one of the most widely used pattern transfer techniques in IC fabrication. Anisotropic etching removes material in particular directions to produce geometric features including sharp corners, smooth surfaces, and deep cavities, in contrast to isotropic etching,

which creates a lower-resolution concave shape behind the photoresist etching mask. During the etching process, a patterned resist layer serves as a mask for a substrate beneath it, such as silicon. Because it can create vertical sidewall profiles with minimal to no undercut, plasma etching is frequently employed to etch nanoscale structures. As shown in the above figure, Anisotropic etching usually produces a cross-section with no undercut.

Diffusion

Diffusion is a process by which atoms move from a high-concentration region to a low-concentration region. This technique is used to insert impurity atoms (dopants) into silicon during the production of VLSI in order to alter its resistivity. The speed at which The rate at which dopants diffuse in silicon strongly depends on temperature. To achieve the required doping profile, contaminants are typically diffused at high temperatures (1000–1200°C). Impurities are virtually “locked” in place when the wafer is cooled to room temperature.

The diffusion process is performed in furnaces similar to those used for oxidation. The depth

to which the impurities diffuse depends on both the temperature and the processing time. A PN junction is created by diffusing boron into an n-type substrate. The diffused layer can also be employed as a conducting layer with extremely low resistance if the doping concentration is high.

Ion Implantation

Ion implantation is the method used to introduce impurities into the semiconductor crystal. The desired dopant is produced as ions using an ion implanter, which then accelerates the ions with an electric field before allowing them to impact the semiconductor surface. The ions are incorporated into the crystal structure. The ion beam’s energy, which is influenced by the accelerating-field voltage, is connected to the penetration depth.

By changing the beam current, the amount of implanted ions can be managed. Ion implantation produces impurity profiles that are significantly more precise and repeatable than those acquired by diffusion because both voltage and current can be precisely measured and controlled. Ion implantation can additionally be carried out in a warm environment.

When accurate control of the doping profile is necessary for device operation. After the ion implantation process, we are doing the Annealing Process, because, after implantation, a thermal diffusion (annealing) is necessary for the removal of the ion-induced damage, the activation of dopants, and the formation of the desired profile shape.

Chemical Vapor Deposition

Chemical vapor deposition (CVD) is a process by which gases or vapors are chemically reacted, and leading to the formation of solids on a substrate. CVD can be used to deposit various materials on a silicon substrate including SiO2, Si3N4, polysilicon, etc. Although the CVD oxide layer’s characteristics are not as good as those of a thermally produced oxide, they are still good enough to allow the layer to function as an electrical insulator.

The oxide deposits more quickly and at a lower temperature with a CVD layer (below 500°C). If the reaction temperature is high enough (over 1000°C), the layer deposited will be crystalline. Such a layer is referred to as an epitaxial layer, and epitaxy rather than CVD is used to describe the deposition process.

The atoms won’t be able to align themselves along the same crystallographic orientation at lower temperatures or if the substrate surface isn’t made of single-crystal silicon. Polysilicon layers are normally doped very heavily to form highly conductive regions that can be used for electrical interconnections.

Metallization

Metallization involves the deposition of metal over the entire surface of the silicon. The purpose of metallization is to interconnect the various components like transistors, capacitors, resistors, etc to form the desired integrated circuit. Next, the necessary connecting pattern is selectively created. etched. Sputtering is commonly used to deposit the metal layer.

In a vacuum chamber, a pure metal disk is positioned beneath an Ar (argon) ion cannon. Additionally positioned inside the chamber above the target are the wafers. The thickness of the metal film can be controlled by the length of the sputtering time, which is normally in the range

of some minutes. The metal interconnects can then be defined using photolithography and etching steps.

Packaging

The final step in VLSI fabrication is packing. A VLSI chip may contain from 10 to more than 108 transistors; each chip is rectangular and can be up to tens of millimeters on a side. The circuits are initially electrically examined using an automatic probing station while they are still in wafer form.

Bad circuits are identified afterward by marking them. The excellent circuits are put in packages once the circuits are divided from one another (by dicing). The pins of the package are typically connected to the metallization pattern on the die using fine gold wires. The packaging is then sealed with plastic or epoxy in a vacuum or inert environment.